Embedded World 2024: Safety & security, HW/SW co-optimization and feminist AI

by Tora Fridholm Step into the buzz and excitement of ew24, where innovation, collaboration, and inspiration converge! In this blog post, we’ll take you on a journey through the highlights and insights from one of the most anticipated events of the year. From groundbreaking technologies to thought-provoking discussions, get ready to dive in and discover […]

Functional safety in the automotive supply chain

By Dave Higham and Maricel Ventura Reliance on electronics and software is big business in the automotive industry and has driven significant focus on quality and reliability of vehicles and their components. Alongside this, the aim of safe, secure and accident-free driving has been given significant attention, with the publication of ISO 26262 for functional […]

From vision to reality in RISC-V: Interview with Karel Masarik

Karel Masarik is the founder of Codasip and since January 2024 also a member of the board of RISC-V International. Recently, EY named Karel Masarik the regional Entrepreneur of the year 2023, which caused another Czech industry veteran, Václav Muchna of Y Soft Corporation, to dub Karel “the chip king”. Founding RISC-V member Where did […]

Saving the planet, one byte at a time

How can Custom Compute participate in getting greener? Sustainability is a hotter topic than ever and Apple just launched its first carbon neutral products. But how can the semiconductor industry contribute? The role of the semiconductor industry We all know something must be done to make our lives, and the products we use, more sustainable, […]

Increasing design skills for custom compute

As discussed in an another blog post by Mike Eftimakis, there are limitations to traditional design methods that use “off-the-shelf” processor cores. Traditionally, software engineers try to fit their code to the constraints of the chosen processor hardware. The alternative is to co-optimize the hardware and software together to create a custom compute solution. You […]

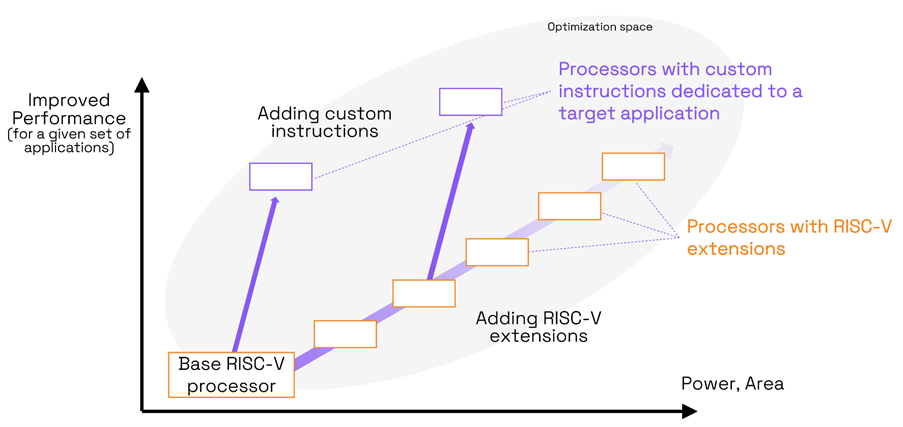

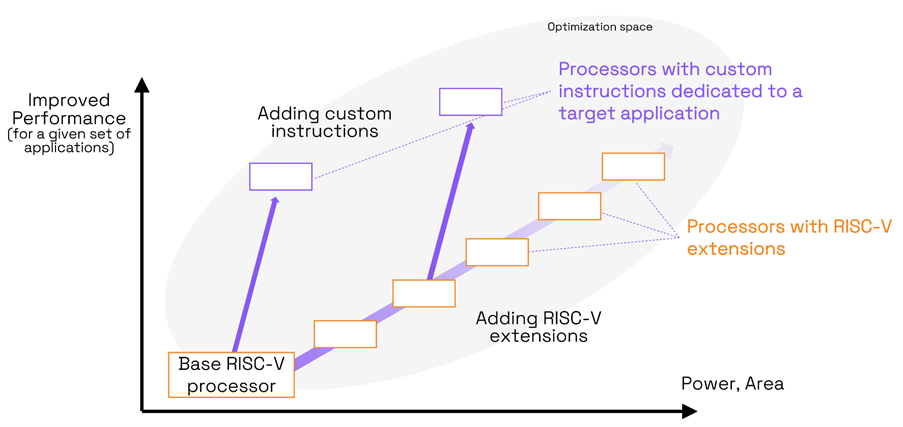

No one-size-fits-all approach to RISC-V processor optimization

As the demand for high-performance processors continues to grow and semiconductor scaling laws continue to show their limits, the need for processor optimization is inevitable. As I explained in a previous blog, RISC-V is designed to enable this. However, there is no one-size-fits-all approach to processor optimization. As each workload and each application will have […]

RISC-V customization, HW/SW co-optimization, and custom compute

Do we still need to introduce and define RISC-V? You know, the open-source instruction set architecture (ISA) that is gaining popularity thanks to its flexibility, scalability, and modularity. Okay, we just did, just to be sure we are all on the same page. One of the key benefits and the main “raison d’être” of RISC-V […]

Highlights from 2022, a turning year for Codasip

The start of a new year is a perfect time to look back and reflect on the previous year and our company’s position. At the RISC-V Summit at the end of 2021, our CEO Ron Black said that Scaling is Failing, with regard to Moore’s Law, Dennard Scaling, and Amdahl’s Law, and the industry needs […]

design automation to drive innovation and differentiation

With semiconductor scaling no longer being an option in most situations, optimization means customizing the processor for your specific application. With the right approach and right tools, processor design automation can enable innovation and differentiation. One way of achieving this is to create an application-specific processor by owning the design. To do this efficiently, manual […]