# Compact CORDIC accelerator implementation for embedded RISC-V core

Alexey Shchekin, Ettore Giliberti

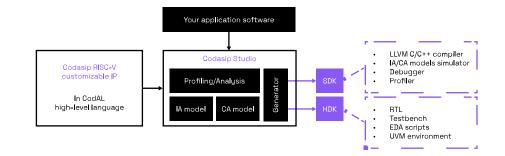

## → Codasip Studio and RISC-V Processors

#### Begin with a standard core

- Embedded and application cores

- High quality, production-ready

- Fully RISC-V compliant

#### Differentiate with Codasip Studio

- · Configure / Customize

- Using CodAL architecture description language

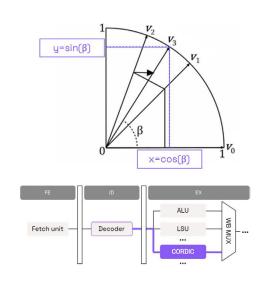

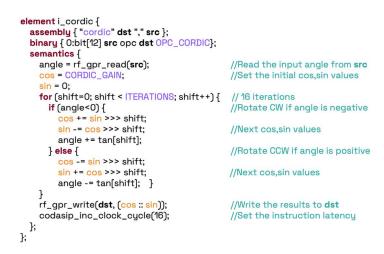

# → CORDIC accelerator implemented with CodAL

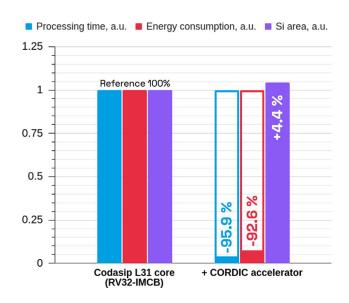

### → How customization affects the PPA

- 1 custom instruction call to start "CORDIC" flow

- 16 cycles to get the result

- 16-bit fixed-point results representation

| (TSMC 28nm)        | RISC-V(L31) | + CORDIC |

|--------------------|-------------|----------|

| Area, a.u.         | 100%        | 104.4%   |

| Performance gain   | 1x          | 24.3×    |

| Energy consumption | 100%        | 7.4%     |

| Design time, lines of code in<br>CodAL |     | Lines of code<br>in Verilog |

|----------------------------------------|-----|-----------------------------|

| 3 person-days                          | 210 | 600 (~3x)                   |