Codasip Studio 9.2が利用可能になりました。独自のプロセッサ設計自動化ツールセットのこの新しいバージョンには、アプリケーションを拡張および最適化する一連の新機能が強化されています。

Codasip Studio 9.2.0でサポートした新機能は次のとおりです:

- マクロ プロセッサ

- CodALの配列サポート

- uRISC-V 2.0 無償サンプル

- モジュール内でのパイプライン定義

- シミュレータの保存状態と復元状態

- RHEL8サポート (Red Hat Enterprise Linux)

- Embedded World 2022 で発表したMacOSのサポート

マクロ プロセッサ、uRISC-V 2.0、およびCodALの配列機能を見てみましょう

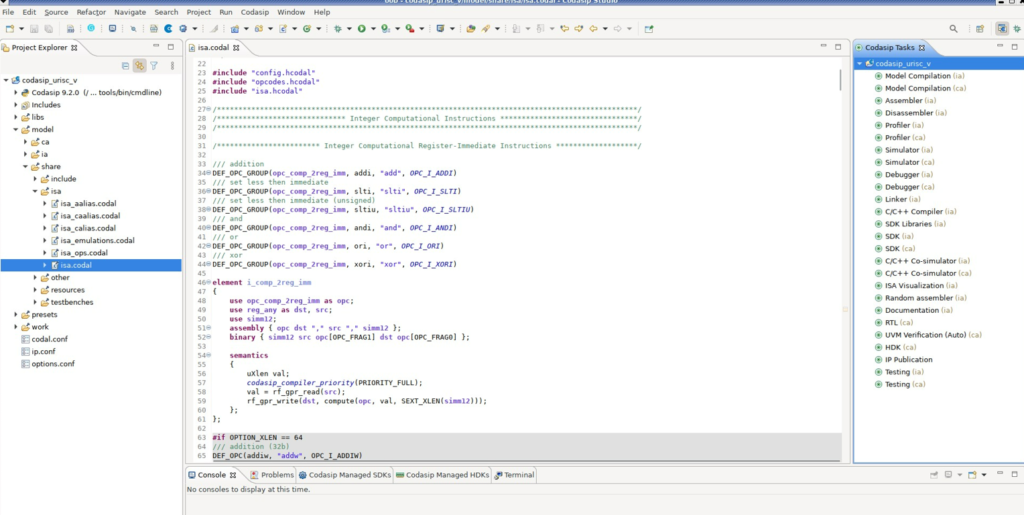

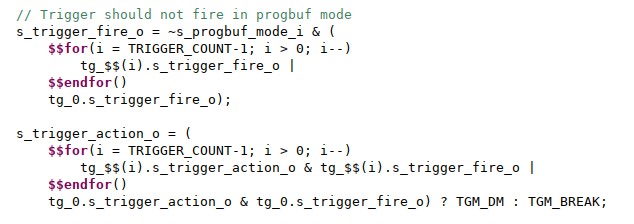

マクロ プロセッサのサポートによるCODAL開発の効率化

Codasip Studio 9.2.0は、マクロ プロセッサ、つまり、コードを生成するための一連のコンストラクトを使用して、CodALモデルの記述を簡素化する強力なテキストプロセッサを搭載しています。C/C++プリプロセッサと比較して、引数付き呼び出し可能なマクロ、ループ、複雑な式などの主要な機能をサポートしています。

マクロ プロセッサは、開発者の作業を簡素化します。不要なオーバーヘッドを生み出す可能性のある作業の繰り返しや関数の呼び出しを避けることができます。次の例は、マクロ プロセッサの使用例を示しています。

なお、マクロ プロセッサは他の言語やツールでも使用可能です。

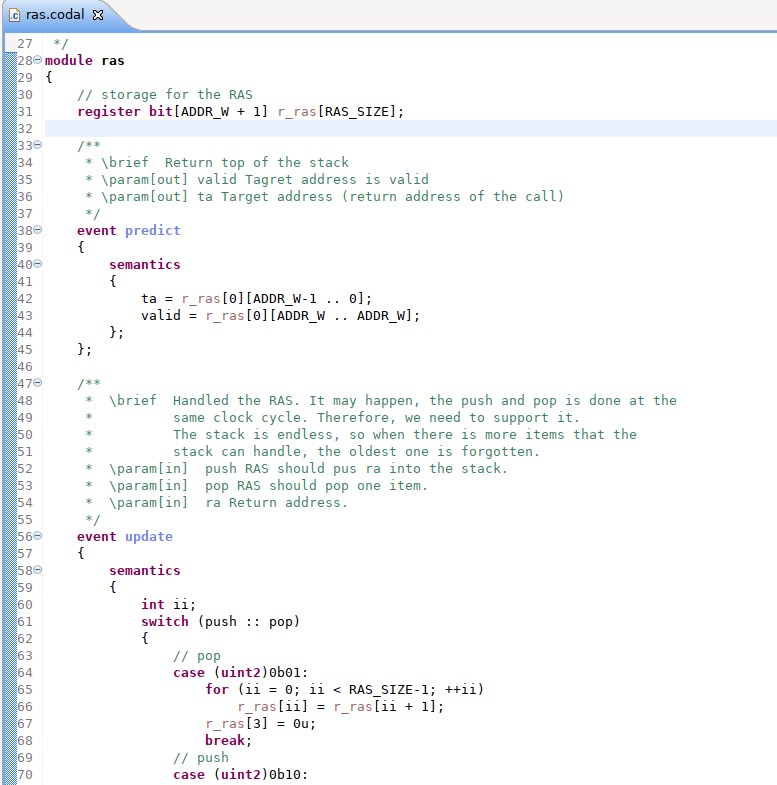

マルチスレッド アプリケーションのためのCODALの配列サポート

Codasip Studio 9.2.0では、マルチスレッド コア用のレジスタとレジスタ ファイルの配列をサポートします。これらの配列は、スレッドごとに情報を保持します。配列のサイズはスレッドの数と一致し、各スレッドには、使用可能な配列内のそれぞれのインデックスのみが含まれます。

Codasip Studio 9.2.0では信号の配列もサポートされていますが、常に同じサイズであり、多次元配列はサポートされていないことに注意してください。配列から配列への代入は、データ型が一対一で一致していれば、リソース型が異なっていてもサポートされます。例えば、レジスタの配列を同じデータ型の信号の配列に割り当てることはサポートされています。

配列は動的にインデックスを付けることができます。ループの場合、配列で使用できるようにセマンティクスが拡張されます。

次の例は、アーキテクチャ リソースの配列構文を示しています。

register bit[32] r_foo [32];

register_file bit[32] rf_foo [FOO_SIZE];

register bit[1] s_foo [ONE + TWO];

URISC-V 2.0実験用サンプル

最初にCodasip Studio 9.0では、5段パイプライン アプリケーション用のuRISC-Vプロセッサをサンプル提供しました。uRISC-Vは、実際のRISC-V実装を確認しながら学習することができるチュートリアルです。Codasip Studio 9.2.0では、このチュートリアルがuRISC-V 2.0となり、3段パイプラインアプリケーションにも対応できるようになりました。

このサンプルにより、Studioっを用いたRISC-Vアーキテクチャの教育や習熟のための可能性が広がります。これは、Codasip社の商用RISC-Vコアと同じ手法で設計されたモデルで、プロセッサの改造、カスタム命令拡張の追加、性能最適化などの実験が可能です。

実装は、RISC-V I (基本整数)、M (整数乗除算標準拡張)、Zicsr (制御・ステータスレジスタ命令)、およびZifencei(フェンス命令)拡張と、RISC-V標準のオンチップデバッガをサポートする、シンプルな32ビットまたは64ビット3段パイプライン プロセッサである。