オープンなRISC-V ISA, 移植可能なソフトウェアは, ドメイン特化型プロセッサを開発する良い出発点です. しかし, ソフトウェアのプロファイリングや, 命令の追加・削除の実験を効率的に行い, 簡単かつスマートにISAを最適化するにはどうしたらよいのでしょうか. ここでは, 既存のRISC-Vプロセッサを効率的にカスタマイズする最適解について考えて行きます.

命令セットを変更する方法

一般的に2つのアプローチが考えられます. 手作業で行うか, 可能な限り自動化するかです.

手作業で臨むアプローチ

命令セットを変更する昔ながらの方法:

- 命令セットシミュレータ(ISS)を修正して, ISAを変更

- 新しいISAを反映させるためにSDKをアップデート

この方法だと, 膨大な量の手作業が必要な上, 手作業によるリスクを伴います. そして完成したSDKでは, カスタム命令を組み込み関数, またはインラインアセンブラ・コードとして利用できるようにすることが殆どです. ソフトウェア開発者にとってより良い開発環境となる, コンパイラを修正・検証するというもう一つの選択肢を実現するためにはかなりの労力を必要とします. 同様に, プロセッサのハードウェア側を拡張する場合, 従来はRTLを編集して, マイクロアーキテクチャを変更し, それをゴールデンリファレンスのISSと照らし合わせて検証する必要があります.

自動化されたアプローチ

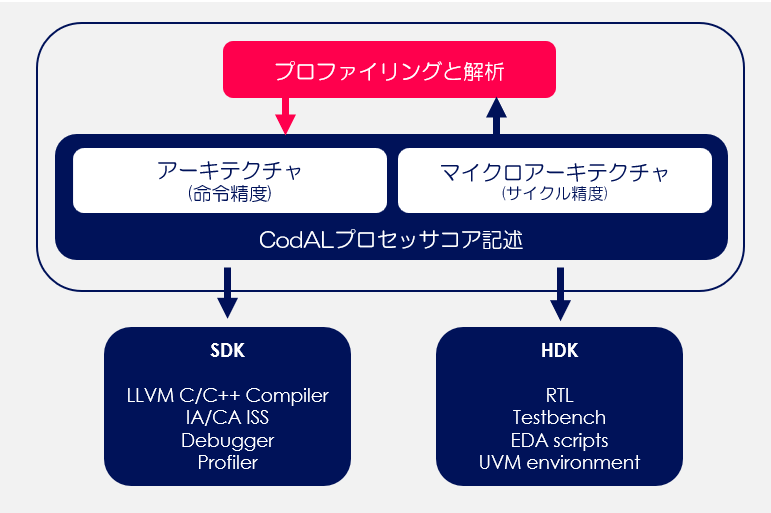

対象的に, CodALのようなプロセッサ記述言語でISAを記述すると, 設計自動化ツールを用いて, このプロセスの効率が大幅に改善されます. Codasip Studioは, 変更後のISAに対応した新しいISSとコンパイラの両方を自動生成できるため, プロセッサのカスタマイズ 作業がより簡単になります. また, CodALのプロセッサ記述言語は, 命令精度の記述だけでなく, マイクロアーキテクチャの記述(サイクル精度)も可能です. 2つのレベルの整合性は, Studio環境内で静的解析により確認できます.

カスタマイズをRISC-V ISAのRTLモデルから始めるよりも, CodALで記述された完全なRISC-Vプロセッサコアから始める方が, はるかに簡単なアプローチです.

CODASIP STUDIOを使用した, RISC-V CPUのカスタマイズ自動化

Codasip RISC-Vプロセッサは, RTLでなく全てCodAL言語を用いてCodasip Studioで開発しています. シンプルな32ビットの組み込み用コアから, 64ビットのLinux対応マルチコア・アプリケーション・プロセッサまで, 幅広いコアを取り揃えています. したがって, パイプライン段数や対応するOSのサポートなど, 必要なベースライン要件を満たすプロセッサを選択し, 貴方はパフォーマンスを向上させるためのカスタム拡張機能の作成に集中することができます. すでに実績のある完成されたプロセッサIPからカスタマイズを始めることで, 新しい命令のためのマイクロアーキテクチャの追加作業に集中でき, 時間の節約とリスクの大幅な低減が可能になります.

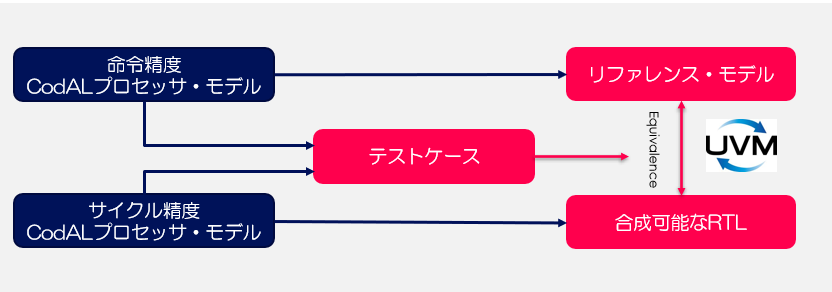

Codasip Studioは, RTL, テストベンチ, EDAスクリプト, UVM環境を含むHDKを生成できます. UVM環境を用い, ゴールデンISSリファレンスとRTLの動的等価性検証が可能となります. 生成されるUVM環境には, レジスタファイル, バスプロトコル, メモリ, キャッシュなどの主な機能領域に対するアサーションとカバレッジポイントが, デフォルトで含まれています. サードパーティのRTLシミュレータを用いて, RTLのファンクションおよびコードカバレッジの達成度も測定することができます.

マイクロアーキテクチャを拡張した後, Codasip Studioプロファイラには, CodALのコードカバレッジ(行, 条件, 式)を評価するためのカバレッジ解析ツールが用意されています. また, Codasip Studioには, ランダム・アセンブラ生成ツールが用意されており, 簡単に包括的にコードカバレッジを評価することができます. 一部困難なケースでは, ダイレクトテストを追加する必要があるかもしれません.

Codasip RISC-Vプロセッサは, CodALソースコードでライセンスされ, Codasip Studioを用いて効率的に改良, 検証を行うことができます. これは, ドメイン特化型プロセッサを作成する上で費用対効果の高い, 非常に効率的なアプローチです.