I was at the Siemens EDA User 2 User conference in Munich last week. This one-day event is the perfect opportunity to learn, grow and connect with technical experts who design innovative products using Siemens EDA tools in Europe. This year’s edition was obviously not disappointing in any way (OK, perhaps the weather could have been nicer!). From the discussions I had to the keynotes and technical sessions I attended, I noticed a pattern. A recurring theme. Something that resonated pretty well with what we do at Codasip: Shifting left for success.

Shifting left for success – the trendy key phrase to adopt?

The term “shift left” is not new. It originated in the software industry and referred to finding and fixing bugs early in the development process rather than catching them during post-release testing, where they are a lot more expensive to fix. Applied to our semiconductor industry, the principle of shift left is taking a broader meaning. Tasks that were traditionally done at a later stage of the process are now performed at earlier stages. Not just bug hunting, not just verification. The reasons for shifting left with semiconductors and processor IPs go beyond this. And how do you efficiently and successfully shift left?

Industry mega trends, increase in design complexity, and scarcity of talents

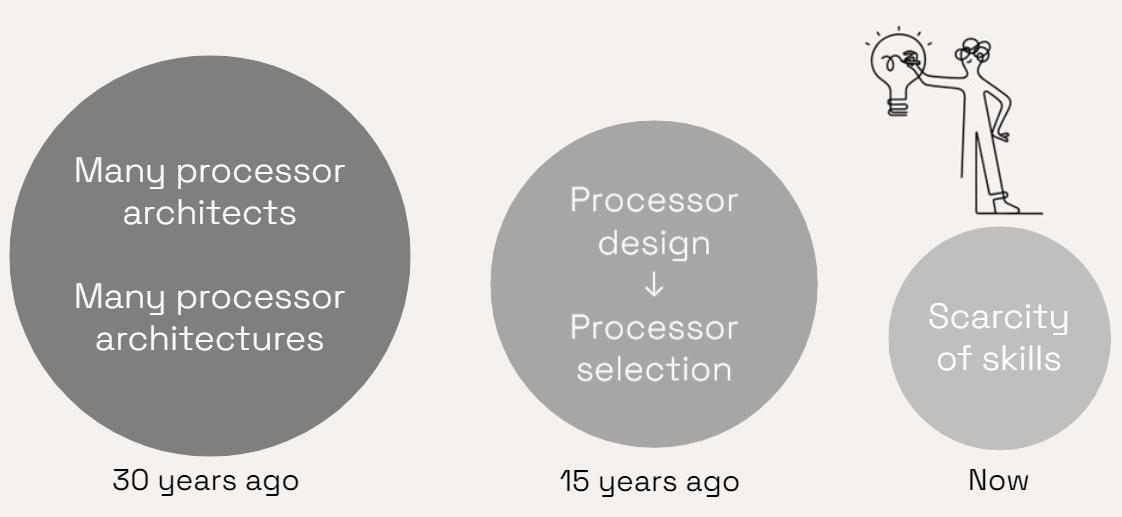

We jumped into the topic right from the keynotes in the morning. From supply chain disruptions to a global pandemic, the past years have shown that the convergence of various mega-trends present opportunities for growth. In other words, technology and economics drive change, and change drives innovation.

Given how data traffic is growing exponentially across all industries and the increasing complexity of electronic systems, traditional approaches do not work anymore. If you want to set your company and products for success, you need to adapt and shift several things to the left. Ensuring functional safety and security is paramount. Ensuring processor quality through best-in-class verification is paramount. Optimizing processor design to address the limits of famous semiconductor industry laws is paramount. Optimizing processes and methodologies to cope with both complexity and scarcity of skills is paramount.

How do you meet the demand for greater computational performance when semiconductor scaling is showing its limits? You innovate architecturally and create more specialized processing units. You customize your compute. And how do you streamline the design process, improve efficiency, and reduce time to market in 2023? How has the industry coped with complexity and limited design skills in the past 50 years?

The answer is automation. The answer is EDA tools.

Hardware & software co-optimization

The intersection of hardware and software design is a key focus in the EDA industry.

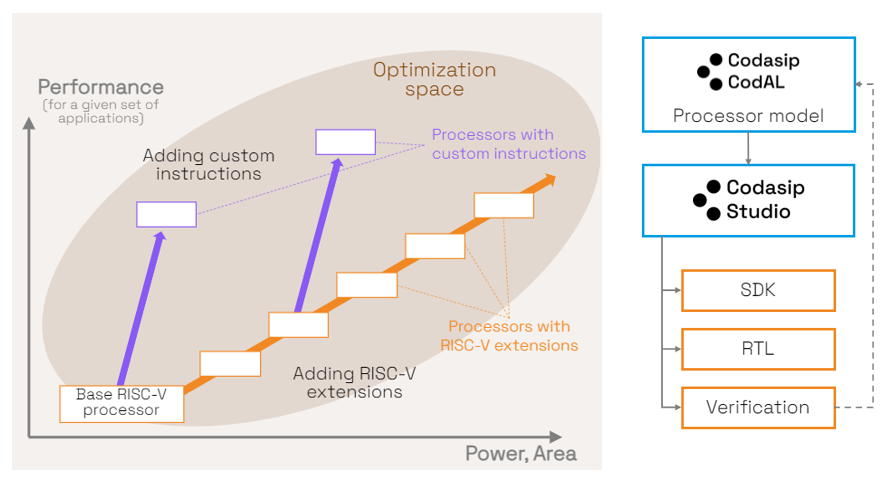

As Mike Eftimakis was discussing in another blog, the traditional approach to hardware design has its limits. What if, instead, you could keep the flexibility of the software while bringing into the processor the additional logic that enables those fantastic speed-ups? This is exactly what the RISC-V open standard is designed for.

One of the key benefits of RISC-V customization is the ability to create custom instructions tailored to specific application needs. You can use custom instructions to accelerate critical operations, reduce memory access, and improve energy efficiency. To pick custom instructions correctly and create efficient implementations, software and hardware teams need to collaborate.

This is what we call hardware and software co-optimization, and it requires a change in methodology. By working earlier on the processor customization, architects on both sides can collaborate from the beginning of the product development. This way, the software team can start developing their critical algorithms and uncover much sooner those potential gains that could not be achieved if the hardware was already frozen.

What if you had…

A starting reference core designed with a tool that you can use to customize the core? This is exactly what we give you at Codasip.

We give you a pre-verified RISC-V core designed in CodAL that you can optimize efficiently using our design automation toolset Codasip Studio. Check it out…!