As a regular attendee of the RISC-V Summit US, I’ve come to appreciate the unique blend of cutting-edge technology discussions and the sunny California weather. Indeed, a welcome departure for a Central European like myself, accustomed to slightly different climates.

Of course, I attended lots of technical sessions as well as the keynotes. I could not help but notice a strong alignment between Meta’s strategy shared in their keynote and our Custom Compute strategy. In fact, the focus on customization throughout the event made this year’s trip an even more pleasant experience than usual. Let me explain why.

Meta said: RISC-V is the way to go

Over the years, I’ve witnessed the RISC-V Summit evolve into a gathering where not only the temperature rises but also the prominence of attendees and speakers. It’s a clear sign that RISC-V, as a technology, is maturing and gaining traction among some of the biggest players in the industry. This year, one keynote caught my attention. Not just because of the company behind it, but because of the profound statements made about the future of RISC-V technology.

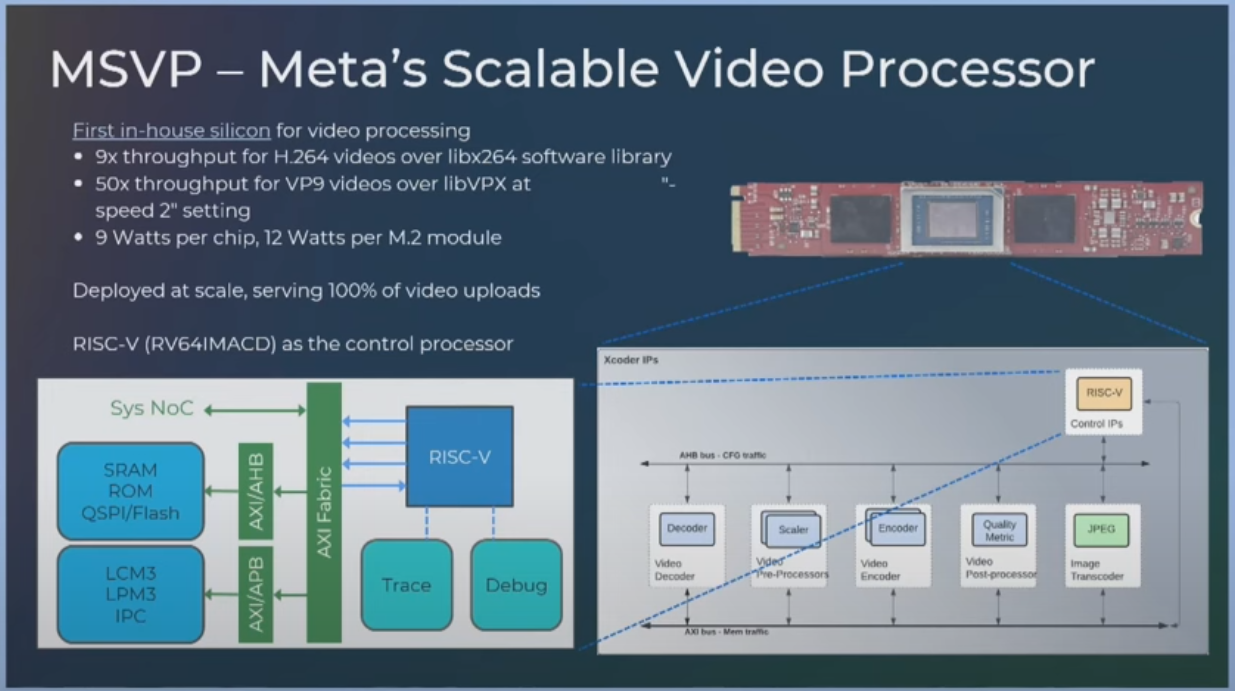

In a world where tech giants shape the course of technological evolution, Meta’s embrace of RISC-V at the RISC-V Summit US speaks volumes. The company revealed plans to implement RISC-V across a spectrum of products. “We’ve identified that RISC-V is the way to go for us moving forward for all the products we have in the roadmap. That includes not just next-generation video transcoders but also next-generation inference accelerators and training chips.”, says Prahlad Venkatapuram, Senior Director of Engineering at Meta. The decision wasn’t just about keeping up with the trends; it was a strategic move to address critical challenges.

Customization is key

Meta emphasized the need for acceleration in business-critical tasks, a demand that couldn’t be met by conventional CPUs alone. The pursuit of power efficiency, performance, low latency, flexibility, and architectural resiliency were the driving forces behind Meta’s RISC-V adoption. But here’s where the plot thickens — even after significant customization, Meta found itself needing more from the existing IP options. “There’s very little in terms of offerings that allow seamless integration of custom instruction and resources into RTP, simulators, software tools and compilers,” Venkatapuram explains. This brings us to the heart of the matter. Meta pointed out a critical gap in the market: the scarcity of offerings allowing seamless integration of custom instructions into key software tools such as simulators and compilers. We could not agree more. In fact, this premise is the basis of our Custom Compute offering.

Codasip Studio is engineered to tackle the very challenges outlined by Meta. It provides a comprehensive solution for the seamless integration of custom instructions into the RISC-V ecosystem. Codasip Studio’s unique value lies in its ability to generate a complete SDK and RTL for customized RISC-V processors, offering not just a piece but the entire puzzle for efficient integration. But let’s come back to that.

Real-world impact: Meta’s success with RISC-V and customization

Meta’s journey with RISC-V, particularly in the realm of video transcoding with the Scalable Video Processor (MSVP), provides a real-world testament to the success of RISC-V customization. By leveraging RISC-V, Meta has replaced a significant portion of CPUs with their custom processors, achieving remarkable efficiency gains.

Now, let’s delve deeper into the intricacies of building a processor with a custom instruction set. It’s not just about implementing the custom hardware; it involves developing a custom compiler as well. Many chip design companies may not have the in-house capabilities for both aspects. This is where the challenges emerge.

The design of a custom processor often goes through a substantial prototyping phase. This is a critical juncture where the flexibility of the processor’s architecture is put to the test. Here’s the catch – developing a custom compiler for a prototype can be a time-consuming process. Imagine the dilemma: you invest time and resources in building a compiler only to realize that the selected custom instructions may not be optimal. This discovery prompts modifications to the compiler, restarting the loop.

This is precisely where Codasip Studio becomes a game-changer. The automation capabilities it offers streamline the prototyping phase, significantly reducing the iteration loop. The efficiency gains come not just from the implementation of custom hardware but from the accelerated development of a custom compiler, simulator and other software development tools. Codasip Studio’s automation makes it feasible to explore different custom instruction sets, fostering a more agile and responsive design process. You can learn more about the possibilities of Custom Compute in our recent technical paper using an example of accelerators for FIR and Median Filters.

Custom Compute is the future of processor design

Meta’s keynote at the RISC-V Summit underscores the evolving landscape of custom processor design. RISC-V’s appeal lies not only in its open architecture but also in its adaptability to unique use cases. Meta’s success highlights the potential, but it also illuminates the challenges.

Codasip, with our Custom Compute offering, stands at the forefront of this evolution. Our solution is not just about meeting current needs; it’s about empowering companies to future-proof their designs. The iterative nature of design and prototyping becomes more manageable with Codasip Studio. So, companies can explore and refine custom instruction sets without the traditional hurdles.

The alignment between Meta’s vision and our Custom Compute approach underscores the importance of a comprehensive solution. A solution that enables harmonious integration of hardware and software. We aim to ensure that the journey of custom processor design is not just feasible but also efficient.