by Tora Fridholm

This blog post summarizes a keynote presentation by our CEO Ron Black at the RISC-V Summit Europe 2024. You can watch a recording of the keynote presentation on RISC-V International’s YouTube channel.

“RISC-V is inevitable” – This is a phrase often used by Calista Redmond, CEO of RISC-V International. Recent research by Omdia and the SHD Group brings objective proof that RISC-V is, in fact, reshaping the future of compute.

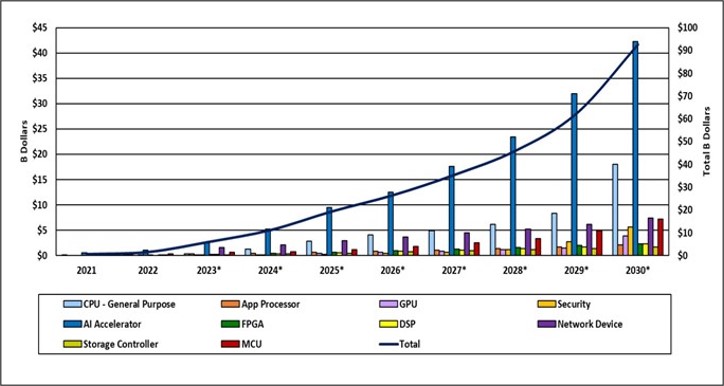

Omdia’s forecast on RISC-V adoption shows that:

- 17 billion RISC-V processors will be shipped in 2030

- RISC-V processors in automotive applications will increase in volume by 66% annually between 2024 and 2030

RISC-V is attractive for many reasons, including its flexibility that opens for customization in a unique way. Of course, there have been some weak points in the past. Let’s address those.

RISC-V challenges

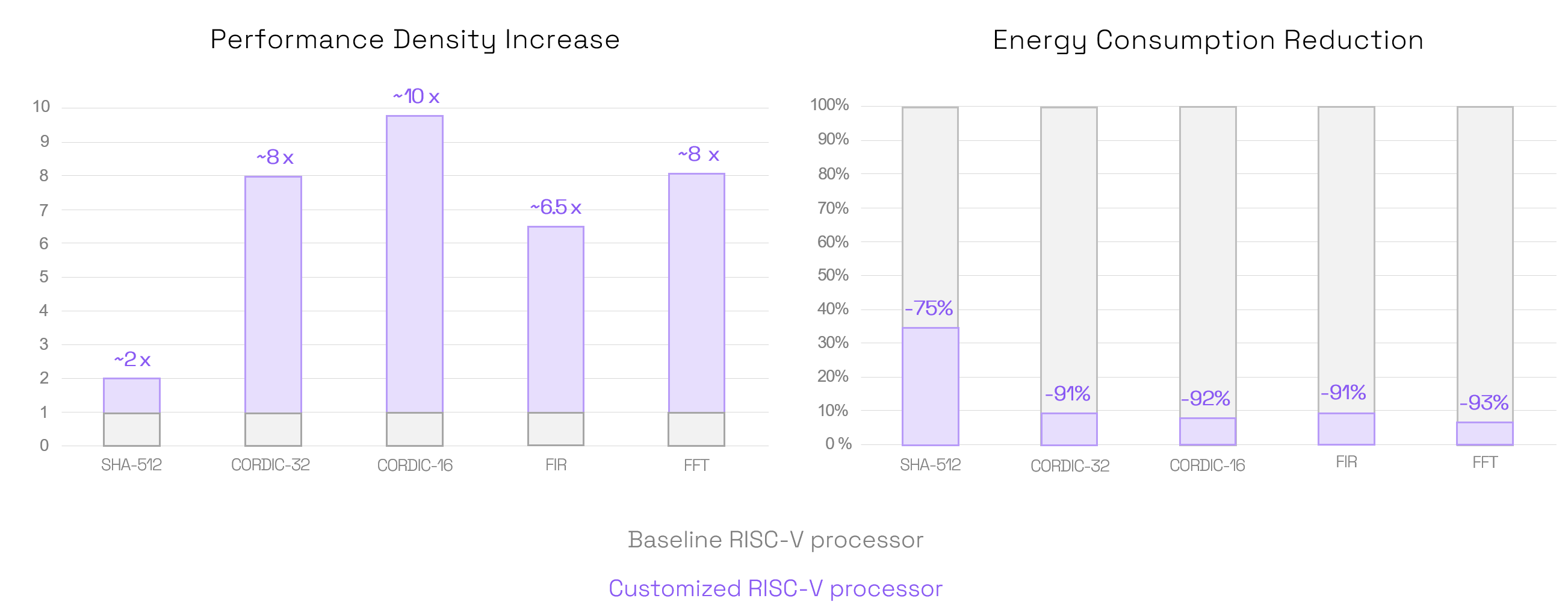

To compare different processor architectures, PPA (Power, Performance, Area) is probably the most straightforward and accessible method there is. By running benchmarks, you get numbers that can be directly compared to other numbers. Is it that easy though? Maybe not. Learn more about why you can’t solely rely on PPA numbers. Rather than comparing PPA numbers for general purpose processors, you can raise the bar for application-specific performance through HW/SW co-optimization. This enables you to achieve performance that is 10x improved, for your specific application.

You could also be concerned about the number of implemented RISC-V designs. Indeed, RISC-V is a young ISA and there just aren’t the same number of designs available yet as for other architectures. Custom Compute can make up for the gap through the rapid creation of application-specific designs.

But perhaps the most pressing issue has been around RISC-V quality and verification. To release products based on custom hardware, you need to make sure that hardware has been thoroughly verified, and that has not been an easy task.

Processor design talent is rare

It’s evident that RISC-V’s open standard provides a great opportunity to democratize the domain-specific processor market. However, over the last twenty to thirty years, the processor market was dominated by general purpose closed architectures. This environment limited processor engineering companies and job prospects.

As Ron put it during his keynote, the cool kids today are data scientists and doing AI. They’re not designing processors. But what if we could make every embedded software developer a processor designer with the help of automation? Well, now we can. We have introduced Bounded Customization in the latest generation of our processor design tool Codasip Studio. With Bounded Customization, the tool protects you from changing things you shouldn’t change. Custom instructions are added on top of the core configuration space. Instruction within bounds cannot harm the baseline core, and therefore you do not need to re-verify the core. In addition, the tool provides an easy-to-use verification framework to verify the custom instructions.

De-risk and speed up core development

As has been noted, Custom Compute brings unmatched benefits for application-specific performance. These capabilities can be fully unlocked by using Codasip Studio Fusion, the 10th version in 10 years of the Codasip Studio tools. The ability to implement custom instructions without risk significantly reduces the barrier to making customizations, and greatly simplifies verification.

By making every embedded software developer a potential processor designer, we believe we have solved the RISC-V puzzle.

In a recent article for Jon Peddie Research, David Harold states:

Despite some initial skepticism, Codasip’s “tools first” business model has proven to have legs, and, arguably, the company is more attractive today than other RISC-V IP rivals like SiFive or Andes. That’s good timing, as the RISC-V IP market is due some M&A activity, we think. The ability to customize within boundaries should both de-risk and speed up core development. Hopefully, the next breakthrough will be to do the same with more powerful cores.