Someone asked me how many Embedded Worlds I’ve attended, and I honestly couldn’t give an exact answer. Is it 10? 12? 15? I’m not sure, but one thing’s for certain: I’m always excited to return. So, what makes this event so special? It’s not just the technical innovations that continue to impress; Embedded World is all about the people. Curious, knowledgeable, and friendly. At one point during the week, four PhDs in Physics were enjoying a lively conversation at our booth. To be fair, some of them were my colleagues, but that kind of interaction isn’t something you experience every day!

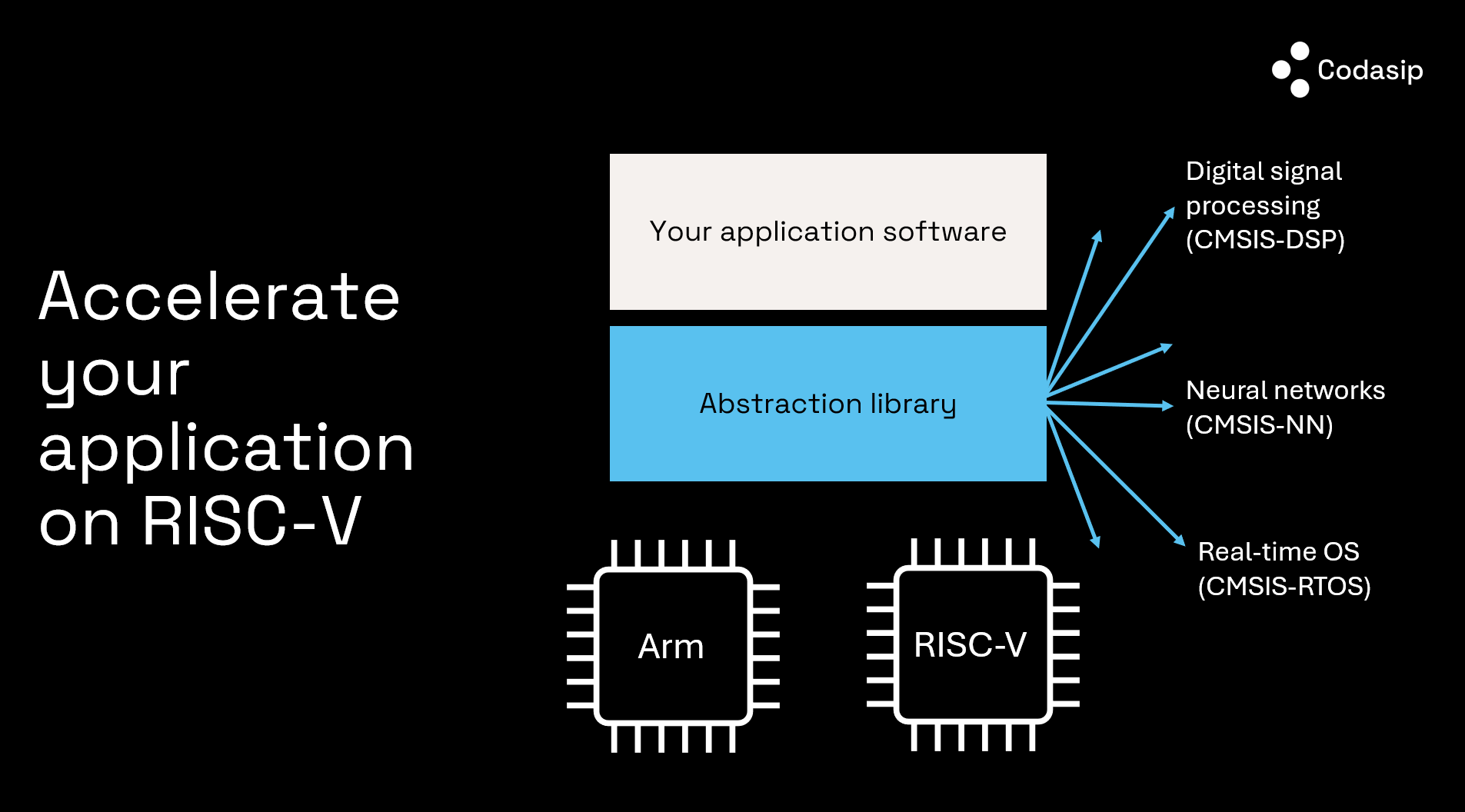

Accelerating neural networks on RISC-V with CMSIS

At the Codasip booth, we showcased an efficient and straightforward method for accelerating embedded applications by porting to RISC-V. We are using CMSIS (Common Microcontroller Software Interface Standard), originally designed to enable Arm applications to run seamlessly across the Arm processor portfolio. By leveraging Codasip’s CMSIS-DSP and CMSIS-NN libraries, we can enable applications developed for legacy Arm cores to run on cutting-edge, domain-optimized RISC-V implementations without the need for any modifications to the software.

What innovative products could you create with performance improvements of 5x, 20x, or even 100x, all at a fraction of the cost? Imagine running more neural network processing on sensor nodes, extending the battery life of mobile devices, or advancing the development of intelligent automotive systems. The possibilities are limitless.

Meanwhile, our CTO, Zdenek Prikryl, delivered a conference session on enabling RISC-V processor customization without the need to re-verify the entire processor. This breakthrough is made possible by our innovative Bounded Customization feature in Codasip Studio.

RISC-V is a force to be reckoned with

Just days before the show, Infineon announced their first automotive RISC-V microcontroller family, and we’re thrilled to see more companies recognizing the immense potential of RISC-V’s open architecture for driving innovation in the automotive sector. This is a nice addition to existing cores from SiFive, Andes and of course or own lineup of certified automotive RISC-V cores. Clearly, RISC-V was a hot topic and with over 25 RISC-V members exhibiting, the community was highly visible throughout the halls, showcasing solutions spanning automotive, AI, IoT, and beyond.

Linux running on CHERI

Speaking of alliances, the CHERI Alliance made its Embedded World debut!

Launched just in November 2024, the alliance showcased a variety of demos from its members, ranging from tiny embedded processors to application cores and data-center-class CPUs. As a proud founding member of the CHERI Alliance, Codasip participated by demonstrating memory-safe CHERI Linux running on our CHERI-enabled X730 core.

Overall, we had an amazing week at Embedded World 2025. With 32,000 visitors, the event once again brought together the majority of the European embedded industry, along with many global attendees, in the beautiful city of Nuremberg. A big thank you to everyone who visited our booth—your discussions, curiosity, and laughter made the event memorable. See you next time!