When designing complex Systems-on-Chip, software teams should be involved early in the process. This will help identify architectural bottlenecks, validate system behavior, and accelerate the entire project timeline. In this process, processor simulation models play a crucial role.

Processor models work as digital representations of a core and are useful from the initial stages of exploration to the later phases of verification. They allow teams to experiment, test, and debug long before silicon is available. The earlier an accurate and usable model is accessible, the sooner potential integration issues surface, and the faster software developers can begin validating code for the target hardware.

A single processor model cannot efficiently serve every need throughout an SoC design project. Designers typically use a spectrum of models depending on the stage of the design. For tasks demanding the execution of substantial software stacks, such as booting an operating system or running complex applications, simulation speed is among the primary needs. This is where solutions like the MachineWare SIM-V instruction set simulator are useful. SIM-V is specifically designed for high-speed simulation of RISC-V processors, making it suitable for scenarios requiring intensive software execution during the pre-silicon phase. The tool is versatile thanks to integrations with standard virtual platform frameworks like SystemC TLM-2.0, and extensions like the open-source VCML.

Tailoring simulation for Custom Compute

At Codasip, we empower design teams to “Architect their ambition” through Custom Compute. This means going beyond off-the-shelf processor IP and tailoring the hardware – specifically the processor core – to optimally execute the intended software workloads. Adding custom instructions to a RISC-V core, for instance, can result in significant gains in performance, power efficiency, and silicon area, creating genuine product differentiation.

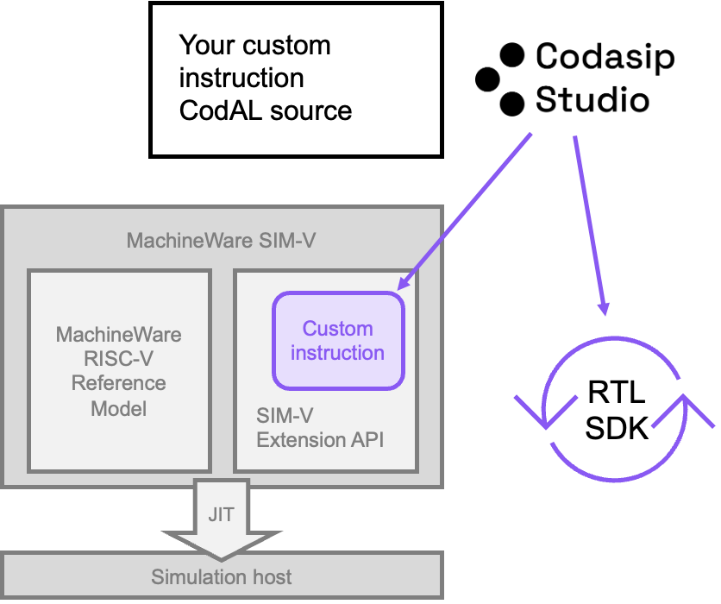

But customization introduces a challenge for standard simulation models. How can a generic model understand and execute instructions that did not exist in the base RISC-V specification? This is where Codasip Studio, our processor design automation toolset, becomes necessary.

Codasip Studio uses the CodAL language to capture the complete definition of a processor’s instruction set architecture and microarchitecture from a single source. You can automatically generate crucial development assets directly from this CodAL description. This includes not only the synthesizable RTL for the hardware but also a full Software Development Kit with compiler, debugger, profiler, and various simulation models – all inherently aware of any custom instructions defined in CodAL. We already provide cycle-accurate simulation models well suited for performance analysis as well as instruction-accurate models, helping for example with debugging of the processor description itself.

Now, we are taking simulation for custom processors a step further.

Introducing SIM-V integration in Codasip Studio

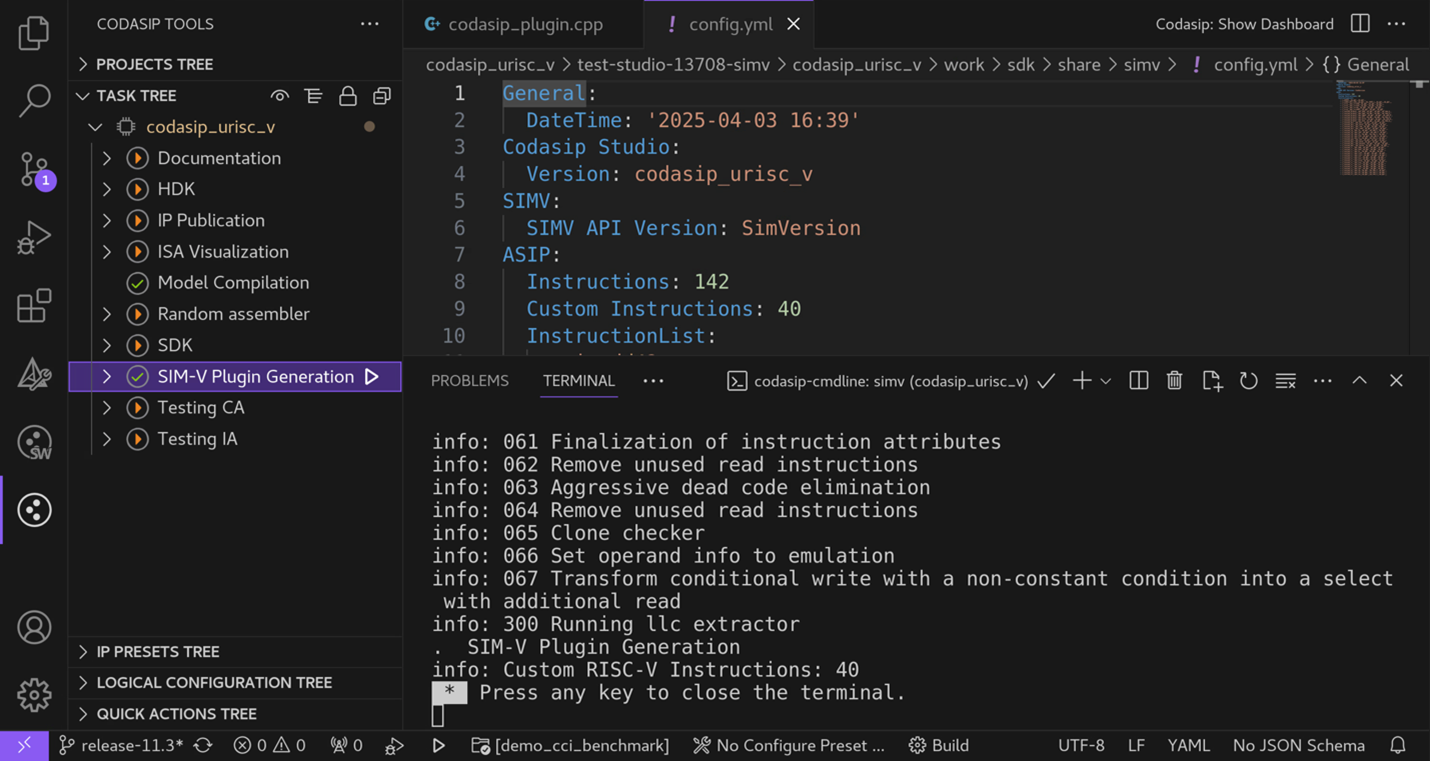

We are excited to announce the latest release of Codasip Studio, packed with features to streamline and enhance the custom processor design journey. One of the feature highlights of this release is the integration with MachineWare’s SIM-V simulator.

Codasip Studio can now automatically analyze a processor design described in CodAL, identify any custom RISC-V instructions defined by the user, and generate an extension for the standard MachineWare SIM-V model. This extension seamlessly integrates with the API of the base SIM-V simulator, enabling it to execute both standard RISC-V instructions and the user-defined custom instructions at high speed.

What does this mean for designers? It means you get the best of both worlds from day one: the rapid simulation speed of SIM-V, essential for complex software workloads, combined with automatic support for the unique custom instructions that differentiate your design. Software teams can now develop, test, and debug their code on a fast, accurate virtual representation of the exact custom processor, much earlier in the design cycle.

What else is new in Codasip Studio?

While the SIM-V integration offers a powerful boost to early software development, the latest version of Codasip Studio release brings several other significant enhancements:

- CodAL meta-programming constructs: We have introduced powerful meta-programming capabilities into the CodAL language. This lets you write more abstract, reusable, and efficient processor descriptions. Repetitive structures or complex parameterized features can now be generated programmatically within CodAL itself, reducing description complexity and potential errors, especially for highly sophisticated core designs. Think of it as adding another layer of automation within the processor description process.

- Bounded Customization for 700 family cores: Our popular Bounded Customization flow, which simplifies the process of adding custom instructions while minimizing verification effort, was previously available for our 100 family of microcontroller-class cores. With this new release, we have extended Bounded Customization support to our higher-performance 700 family of application and embedded cores. This makes it significantly easier for teams using these more powerful cores to leverage the benefits of Custom Compute – adding specific instruction set extensions without requiring deep microarchitecture ability or extensive verification overhead.

Architecting your ambition, faster

The journey to differentiated silicon requires not only innovative processor architectures but also efficient, automated design flows. The latest release of Codasip Studio embodies this principle. By integrating fast simulation support for custom instructions via MachineWare SIM-V, introducing advanced CodAL meta-programming, and extending the accessible Bounded Customization flow to higher-performance cores, we are providing you with even more powerful tools to innovate.

Matching hardware to software through Custom Compute delivers tangible benefits in performance, power, and area. With these new Codasip Studio capabilities, we continue to lower the barriers to entry for processor customization, enabling more teams to build uniquely optimized RISC-V solutions and truly architect their ambition.