Electric motors are at the core of many automotive innovations; from high-efficiency powertrain and steer-by-wire systems to regenerative braking and active suspension. Whilst standard RISC-V embedded cores provide general baseline capabilities, performance, power, and cost can be optimized by adding dedicated custom instructions.

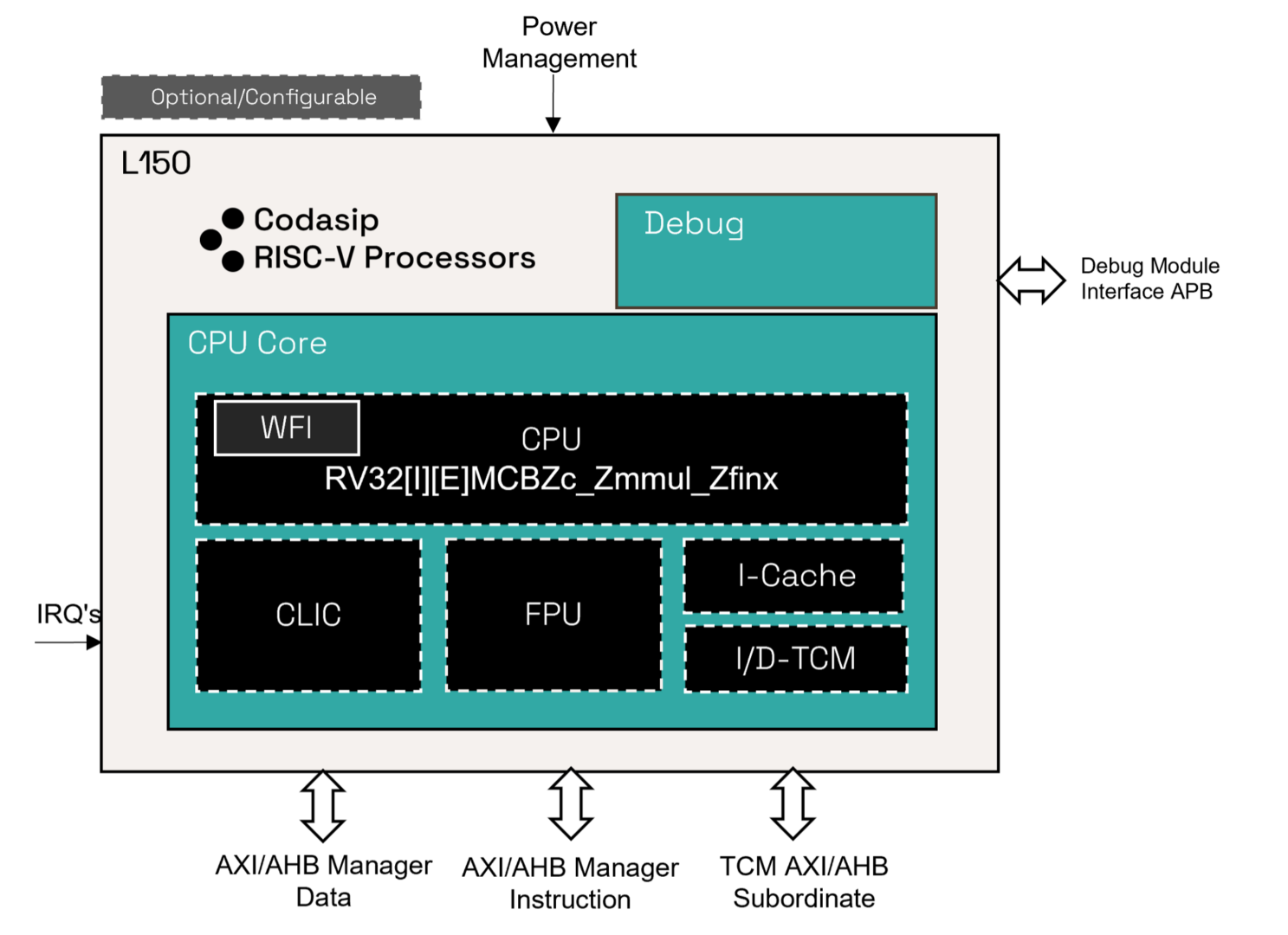

In this blog, we introduce the new Codasip L150: a 3-stage, 32-bit RISC-V core designed for real-time embedded applications where area and power efficiency are critical. Beyond its efficient baseline architecture, the L150 enables domain-specific optimization through Bounded Customization.

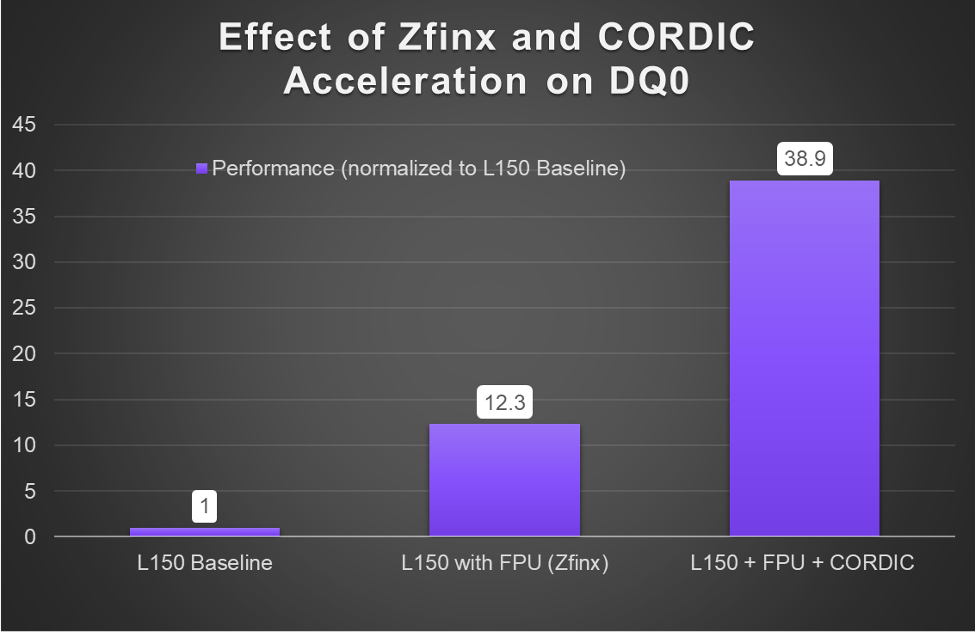

As an example, we’ll examine the DQ0 transformation—a critical sub-function within the motor-control algorithm for automotive applications. By deploying an area-efficient floating-point unit (FPU) implementing the Zfinx RISC-V extension, combined with a CORDIC hardware accelerator Codasip L150 achieves around 39X performance improvement, with only a minimal increase in silicon area.

Codasip L150: built for efficiency and seamless acceleration

Codasip L150 is the latest addition to our 100 family of embedded RISC-V IP cores, recognized for their standout area and power efficiency. Designed with real-time and performance-sensitive applications in mind, Codasip L150 strikes a strong balance between small area and scalable performance.

The core includes several enhancements uplifting the 100 family capabilities, including:

- An area-efficient floating-point unit (FPU) implementing the Zfinx RISC-V extension

- Support for tightly coupled memory (TCM) and configurable instruction and data caches

The inclusion of the Zfinx RISC-V extension, part of the RISC-V standard, enables floating-point operations using the existing integer register file. It is a compelling trade-off for the cost- and energy-effective embedded systems that still need floating-point capabilities without the burden of the entire F extension support. Zfinx RISC-V extension eliminates the need for a dedicated floating-point register file, simplifying the hardware and lowering both area and power consumption. At the same time, the ability to utilize floating-point instructions reduces code size, minimizes clock cycles, and delivers meaningful improvements in performance for the workloads that use real numbers.

Codasip L150 also serves as a versatile baseline for further domain-specific optimization. Its architecture is well-suited to enable acceleration of DSP and AI tasks, making it ideal for workloads beyond motor control, such as sensor fusion or real-time signal processing. With Bounded Customization, engineering teams can introduce accelerators by adding custom instructions and optimizing memory access patterns, without modifying the core’s execution pipeline.

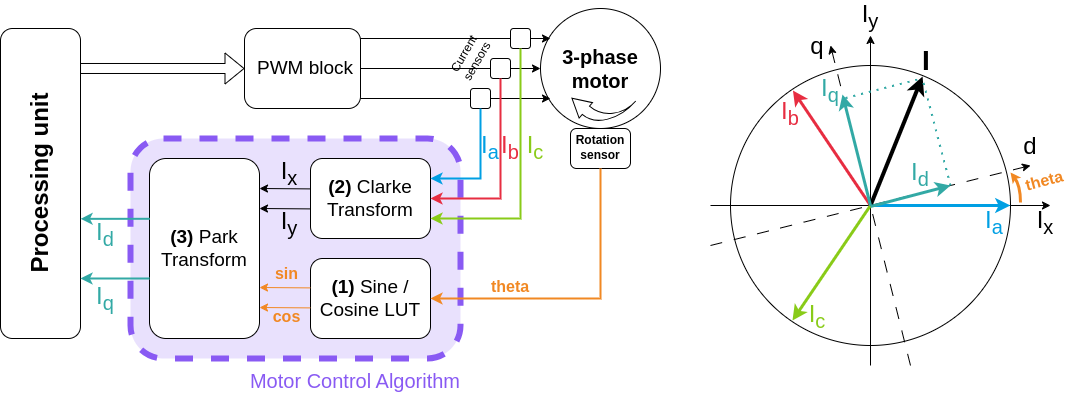

The role of DQ0 transformation in motor control

In automotive Field-Oriented Control (FOC) systems for three-phase motors, the DQ0 transformation is a core mathematical function. It translates three-phase AC signals into a rotating reference frame, yielding Id and Iq components that can be independently controlled. This is critical for efficiently managing torque and magnetic flux in electric motors.

The transformation depends on repeated sine and cosine calculations, often in high-frequency control loops. While Codasip L150’s FPU delivers a 12.3X performance improvement over a L150 baseline (without FPU), significant additional gains come from off-loading the trigonometric operations to dedicated hardware.

Bounded Customization and the CORDIC hardware accelerator

This is where Bounded Customization comes in as it enables the insertion of application-specific enhancements, such as custom instructions and additional compute modules, without altering the processor’s pipeline.

In our DQ0 use case, we added a CORDIC (Coordinate Rotation Digital Computer) module to process custom instructions. This dedicated hardware unit computes sine and cosine in a 32-bit fixed-point format, tailored specifically for the algorithm’s needs.

The outcome:

- The L150 with FPU achieves 12.3X performance improvements over the L150 without FPU.

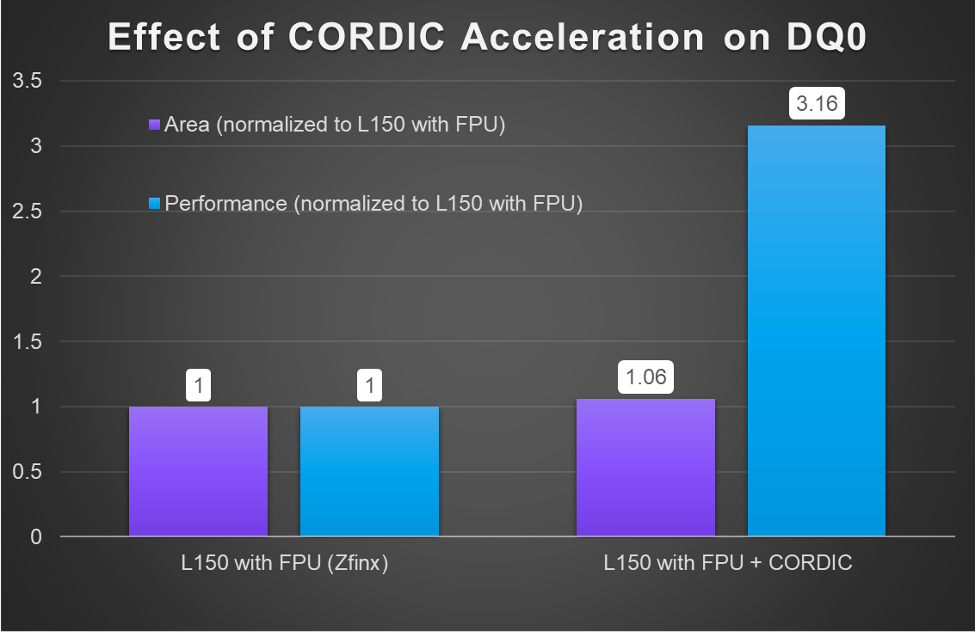

- The introduction of the CORDIC hardware accelerator enables more than 3X the performance of the L150 with FPU, with a total only 6% area impact.

- In total, we achieved 38.9X improvement over the baseline performance of the L150 with no FPU.

These gains are substantial with the added advantage of being achieved without the time, cost, or verification effort expected for a fully custom processor design.

It’s worth noting too that the same hardware accelerator computes tangent and square root as well, enabling re-usability outside the specific DQ0.

Benefits of Bounded Customization for motor control

- Accelerated performance for time-critical tasks

With the CORDIC accelerator targeting hot spots like sine and cosine computation, control loops execute faster, enabling more precise and responsive motor behavior. - Lower power consumption

Optimized execution paths allow the processor to complete its workload sooner and spend more time in low-power states, which is critical for energy-sensitive systems. - Minimal area overhead

Adding a CORDIC accelerator via Bounded Customization only increases silicon area by 6%, a small trade-off for the significant speedup achieved. - No-risk customization

Because Bounded Customization doesn’t alter the core’s pipeline, it avoids many of the risks typically associated with processor design changes. This ensures that the verification claims remain valid facilitating the functional safety case. - Aligned hardware and software toolchains

Codasip Studio generates the RTL and SDK from a single processor description. So, when you customize the hardware, your toolchain updates automatically, saving engineering time and avoiding mismatches.

Conclusion: domain-specific customization without the cost and time overhead

Codasip L150 offers an ideal combination of embedded efficiency and targeted performance. By leveraging Bounded Customization, developers can go beyond general-purpose design and build processors optimized for the workloads that matter most, like motor control.