From guesswork to guidance: Mastering processor co-design with Codasip Exploration Framework

For decades, the art of designing complex System-on-Chips (SoCs) has been a delicate balancing act. The intricate dance between hardware and software, known as co-design, has been guided primarily by the seasoned experience of architects. They navigate a vast, multidimensional space of possibilities, where every tweak to a hardware configuration or a line of software […]

Beyond design automation: How we manage processor IP variants with Codasip Studio

If you’ve been following us at Codasip, you know we’re all about enabling Custom Compute. The power to shape processor hardware to get the best out of your software is, as we see it, key to standing out and getting that crucial edge in performance, power, and area. A big part of what we offer […]

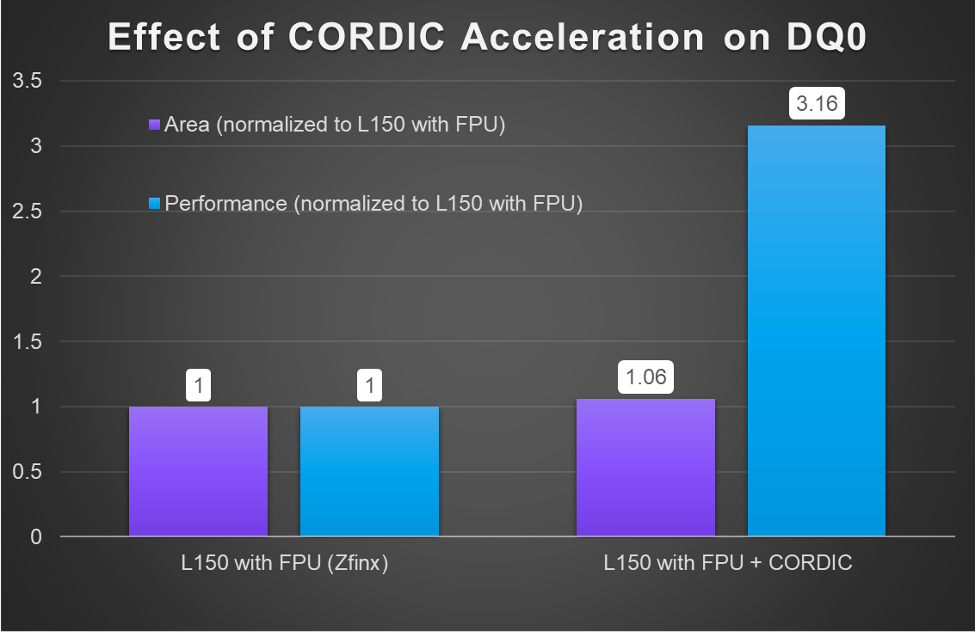

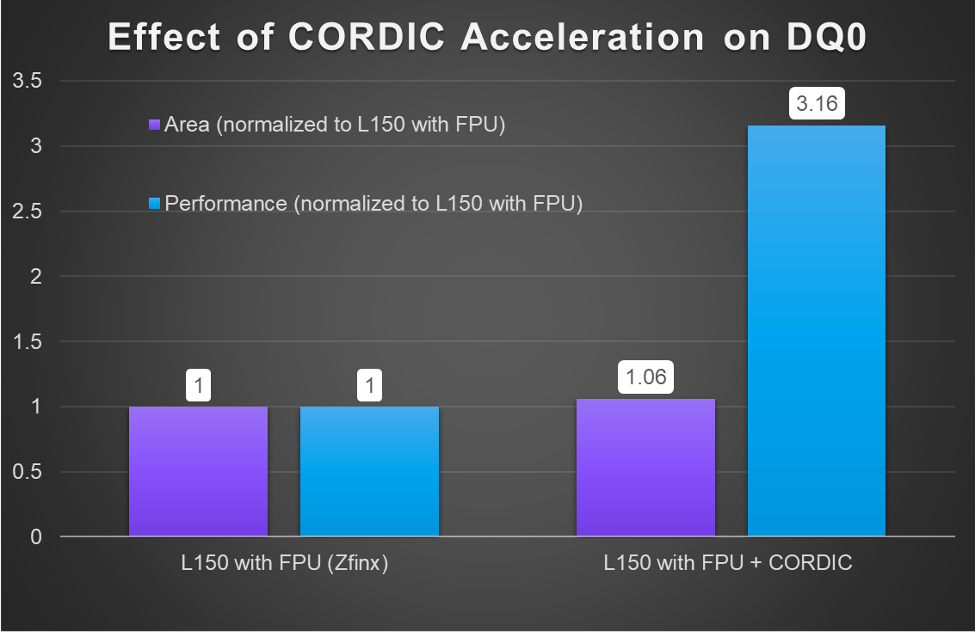

Bounded Customization in action: Codasip L150 and CORDIC acceleration for motor control

Electric motors are at the core of many automotive innovations; from high-efficiency powertrain and steer-by-wire systems to regenerative braking and active suspension. Whilst standard RISC-V embedded cores provide general baseline capabilities, performance, power, and cost can be optimized by adding dedicated custom instructions. In this blog, we introduce the new Codasip L150: a 3-stage, 32-bit […]

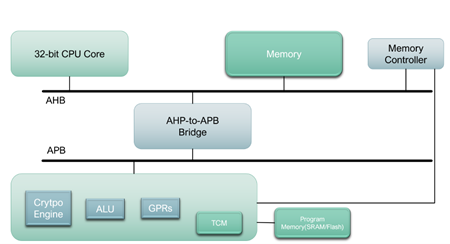

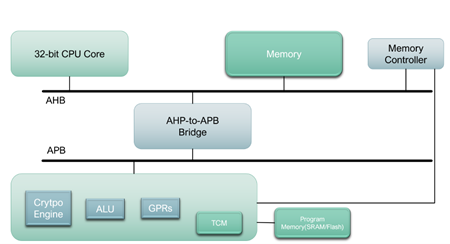

Design and implementation of a hardened cryptographic coprocessor for a RISC-V 128-bit core

Cryptography is a way of encoding and decoding information to guarantee its confidentiality and protection from unauthorised individuals. Within the realm of digital security and cryptographic algorithms, digital signatures play a critical role in establishing trust. Analogous to a physical signature, digital signatures leverage cryptographic algorithms to generate a unique mathematical fingerprint linked to the […]

Neural networks and human-to-human interfaces at Embedded World 2025

Someone asked me how many Embedded Worlds I’ve attended, and I honestly couldn’t give an exact answer. Is it 10? 12? 15? I’m not sure, but one thing’s for certain: I’m always excited to return. So, what makes this event so special? It’s not just the technical innovations that continue to impress; Embedded World is […]

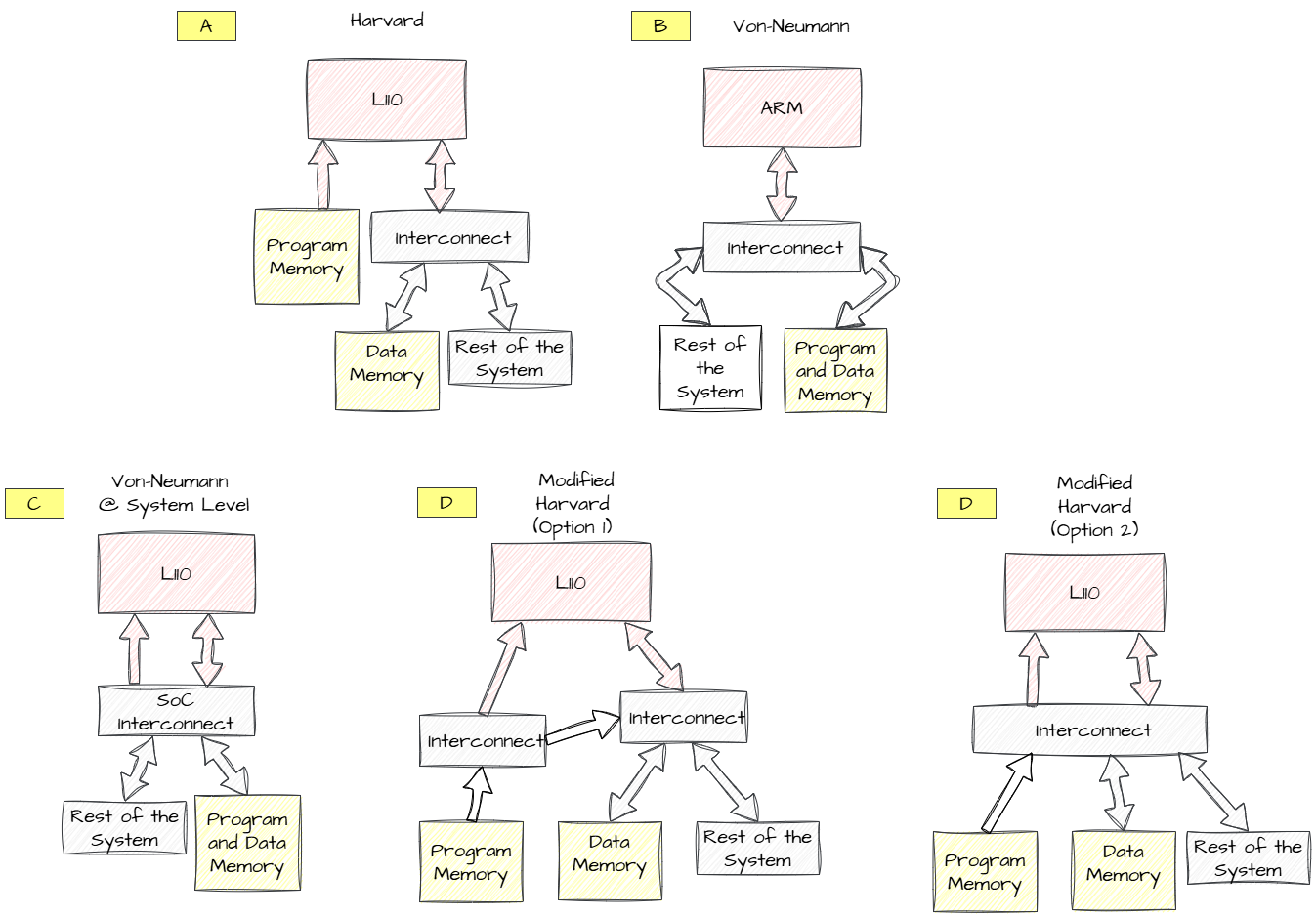

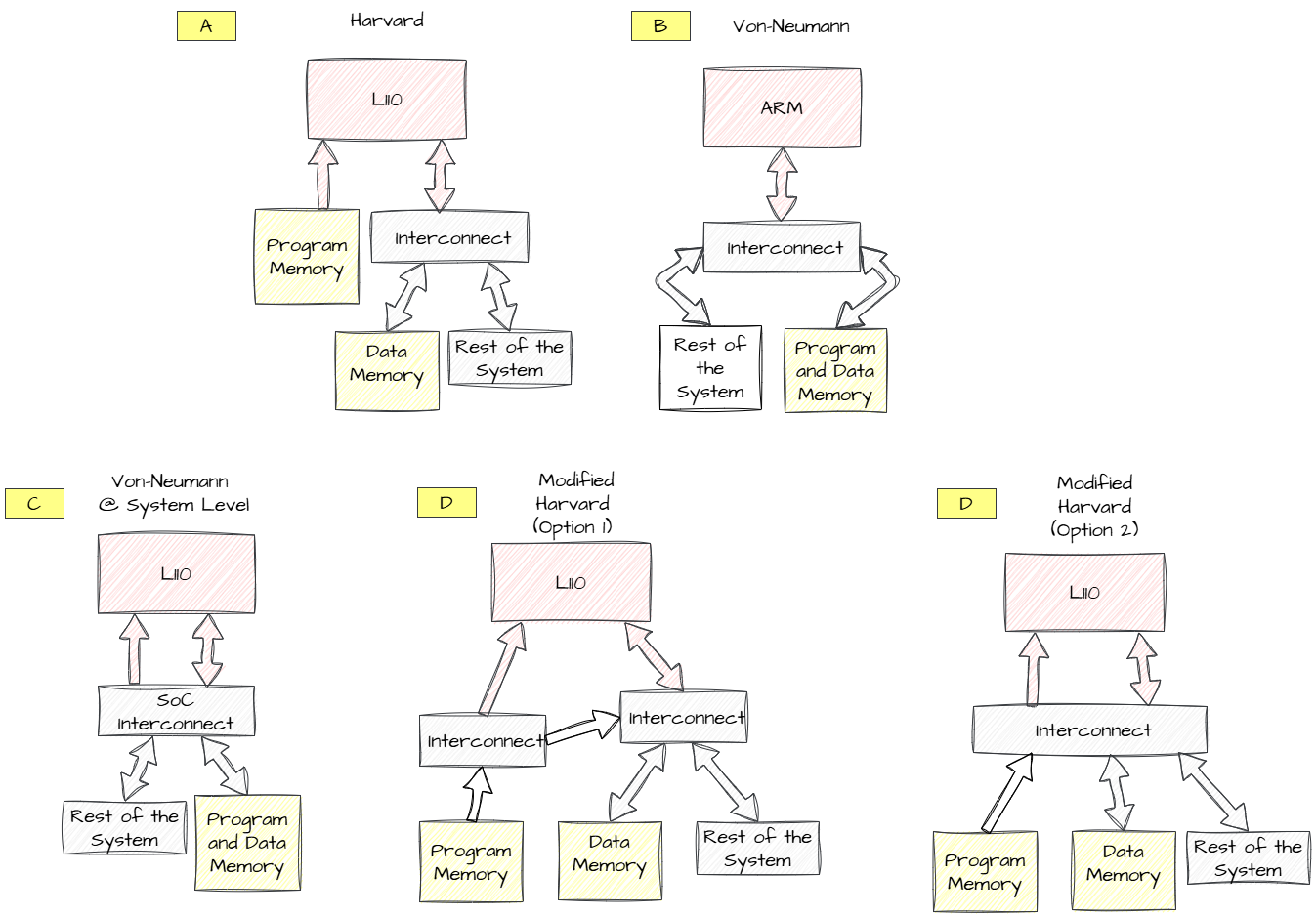

Easy migration from Arm to RISC-V: an L110 case study

Last June, we launched the Codasip L110 RISC-V core, introducing the best-in-class solution for power-efficient applications. The L110 is highly competitive in terms of power efficiency and code density. Additionally, it is the first RISC-V core to support easy and risk-free customization while minimizing the verification effort required to bring these customizations to silicon. Since […]

Securing a 4G-connected Smart Meter Gateway with CHERI

By Mike Eftimakis (Codasip) and Imad Mikaiel (Sequans) In today’s increasingly connected world, securing critical systems like the electrical grid, telecommunication networks, and industrial infrastructure is more important than ever. These systems, connected to the cloud and forming a critical part of a country’s infrastructure, are prime targets for cyberattacks. Governments with a concern for […]

DeepSeek’s aftermath: Lessons to learn as the dust settles

The Chinese AI company DeepSeek took the technology industry, and Wall Street, by storm with its language model achieving a reported 10x higher efficiency than AI industry leaders. You have seen the news and might be getting sick of the endless articles tagging onto it, but I would like to offer a different perspective. DeepSeek claimed […]

Cosmic Compute at the RISC-V Summit North America Hackathon

We had the pleasure of sponsoring and hosting a hackathon at the RISC-V Summit North America 2024 in Santa Clara, California. As part of our commitment to advancing CPU design, we invited participants to take on a challenging technical mission that tested their skill through Codasip Studio, our advanced design tool. This tool, along with […]