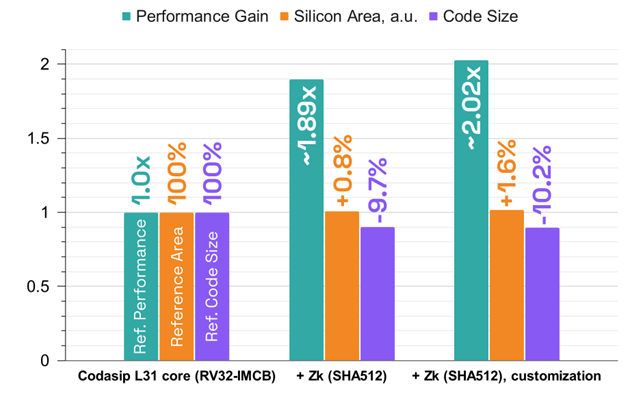

Effectively hiding sensitive data with RISC-V Zk and custom instructions

Cryptographic hash functions play a critical role in computer security providing a one-way transformation of sensitive data. Many information-security applications benefit from using hash functions, specifically digital signatures, message authentication codes, and other forms of authentication. The calculation of hash functions such as SHA512, SHA256, MD5 etc is a potential playground for Custom Compute. This […]

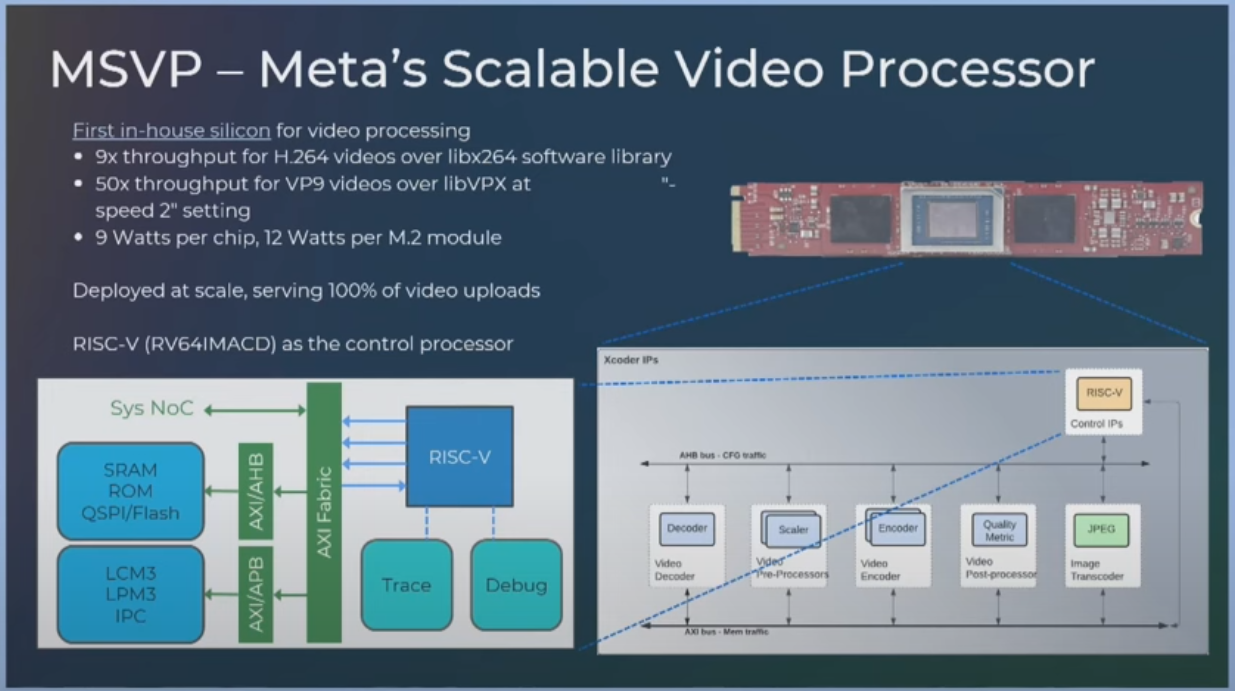

RISC-V Summit report: Meta leads the way for custom processors

As a regular attendee of the RISC-V Summit US, I’ve come to appreciate the unique blend of cutting-edge technology discussions and the sunny California weather. Indeed, a welcome departure for a Central European like myself, accustomed to slightly different climates. Of course, I attended lots of technical sessions as well as the keynotes. I could […]

Codasip’s Expanding RISC-V Offering

In the last three months, Codasip’s RISC-V processor offering has expanded considerably. For some years, Codasip has supplied Bk3 and Bk5 RISC-V cores aimed at low- to medium-complexity embedded applications. But recently four additional cores have joined the Codasip RISC-V offering.

Codasip Presence at Upcoming Events: China Roadshow, DAC 2019, and RISC-V Workshop Zurich

Munich, Germany – May 6th, 2019 – Codasip GmbH, the leading supplier of configurable RISC-V® embedded processor IP, is going to be featured at three major industry events around the globe in the second quarter of 2019: China Roadshow 2019, Design Automation Conference in Las Vegas, and RISC-V Workshop in Zurich. “Getting Started with RISC-V” […]

Codasip to Demonstrate Technology Leadership and Commitment to Open Standards at Taiwan RISC-V Workshop

Munich, Germany – March 7th 2019 – Codasip GmbH, the leading supplier of configurable RISC-V® embedded processor IP, will address the topics of RISC-V C compiler optimizations and frameworks for ISA compliance in two presentations at the upcoming RISC-V Workshop in Taiwan. In the first presentation, Codasip CTO Zdeněk Přikryl will demonstrate how Codasip generates and […]

Vidtoo Technology Licenses Codasip’s Bk3 RISC‑V Processor for High‑Performance Computing SoC

Munich, Germany – December 17th 2018 – Codasip, the leading supplier of RISC-V® embedded processor IP, announced today that Vidtoo Technology, a leader in semiconductor products for machine learning and high-performance computing, has selected Codasip’s Bk3 processor for future HPC chips. Vidtoo Technology, based in Hangzhou, China, focuses on high-bandwidth, high-performance, high-connectivity, artificial intelligence platforms and inference […]

Mythic Chooses Codasip to Deliver RISC-V Computing in their Revolutionary Neural Network Platform

Campbell, California – December 10th 2018 – Codasip, the leading supplier of RISC-V® embedded processor IP, announced today that Mythic, a leader in artificial intelligence (AI) computing technology, has selected Codasip’s configurable Bk3 processor and Codasip Studio for future neural networking chips. Mythic, based in Redwood City, California, and Austin, Texas, will deliver powerful, life-enhancing AI solutions […]

Codasip Releases Studio 8, a Breakthrough in RISC-V Automation, and the Bk7 RISC-V Processor Core for Real-Time Computing Applications

Munich, Germany – December 6th, 2018 – CodasipGmbH, the leading supplier of RISC-V® embedded processor IP, announced today the latest version of Studio, a suite of tools optimized for the development and verification of RISC-V processors, and the Bk7 processor, the first Codasip RISC-V core optimized for Linux and real-time performance. “As the RISC-V ISA specification evolves and […]

Codasip Expands its Global Reach by Signing Channel Partnerships throughout Asia

Campbell, California – September 10th 2018 – Codasip, the leading supplier of RISC‑V® embedded processor IP, today announced that it has signed new reseller representative agreements with leading firms in China, Taiwan, Japan, and India. New strategic partnerships were formed with Shanghai Jiatao, Maojet Technologies of Taiwan, Delphinium Technologies of Bengaluru, India, and Japan Marketing Office […]