The mission

Empowering future innovators: We equip students to tackle cutting-edge challenges in processor architecture, security, AI/ML, safety, advanced memories, and specialized applications.

Solving tomorrow’s challenges: We actively forge partnerships with tech leaders and academia to pioneer solutions for tomorrow’s technological frontiers.

Accelerating innovation: Our dynamic ecosystem features knowledge hubs, online courses, RISC-V gatherings, and hackathons, fueling fresh ideas and breakthroughs.

Through support of students and researchers, the Codasip Labs University program aims to prepare the people and advance the technologies to solve tomorrow’s technological challenges

Collaboration types:

Educational: We offer undergraduate and graduate curricula, along with customizable tools and teaching IPs, empowering faculty in electrical engineering, computer science, and computer engineering to enhance their teaching and laboratory work.

Student exploration: We provide students with access to our cloud-based IDE tools, allowing them to delve into CPU design and application acceleration. Whether for individual exploration or as part of a Masters’ thesis, we encourage hands-on research and experimentation.

Joint research: Through joint research projects, we collaborate with researchers and students, providing them with access to cutting-edge tools, materials, and IPs. Together, we drive innovation and push the boundaries of knowledge.

PhD research sponsorship: We offer partial or full financial support for PhD candidates conducting research aligned with our mutual interests. By leveraging our tools and IPs, we empower them to explore new frontiers and make significant contributions to their fields.

Students, faculty and researches have access to the following:

Cloud-based Codasip Studio Integrated Development System (IDE)

When required and appropriate, local Codasip Studio licenses

Codasip’s high-Level Synthesis Language, CodAL, and Codasip Studio technical support through Codasip

Access to Codasip technologies including computer security, functional safety, artificial intelligence, and domain specific applications

Where appropriate, RISC-V IP cores for research development

Technical support and joint research possibilities with Codasip Labs’ engineers

How do we start?

Online Curriculum Roadmap:

A targeted set of sixteen Codasip online courses are planned. The same course can appear in multiple specializations in that a specialization signifies that a person has completed a set of three or more courses in a single topic. A specialization certificate of completion can be awarded.

Each course will include four one-week modules of content and assignments. A module should be completed in four to six hours resulting in a month course requiring sixteen to twenty-four hours to complete. A specialization of three courses is estimated to take forty-eight to seventy-two hours of work.

Standalone course: Introduction to RISCV

Specialization: CodAL3

- Course: Introduction to Codasip Studio and CodAL3

- Course: Power of abstraction through automation

- Course: Adding custom instructions and resources for embedded processors

Specialization: Advanced CodAL3

- Course: Developing multi-core solutions in Codasip Studio

- Course: Adding custom instruction and resources across multiple pipeline stages

- Course: Implementing multi-issue cores

Specialization: Getting the most out of your Optimized RISCV core

- Course: How to define the software/hardware interface for 2-10x optimization

- Course: Optimize a design through Custom Bounded Instructions (CBI)

- Course: Acceleration through full custom instructions

Specialization: Realizing your Custom Compute processor core

- Course: Implementing System-On-Chip components into your Codasip project

- Course: Integrating RTL components into your Codasip CodAL3 core project

- Course: Developing multi-core solutions in Codasip Studio

Specialization: Realizing your Custom Compute processor in a FPGA

- Course: Realizing your core in FPGA

- Course: Developing and debugging your RISCV FPGA core

- Course: Customizing your RISCV to accelerate your FPGA based application

Success Stories:

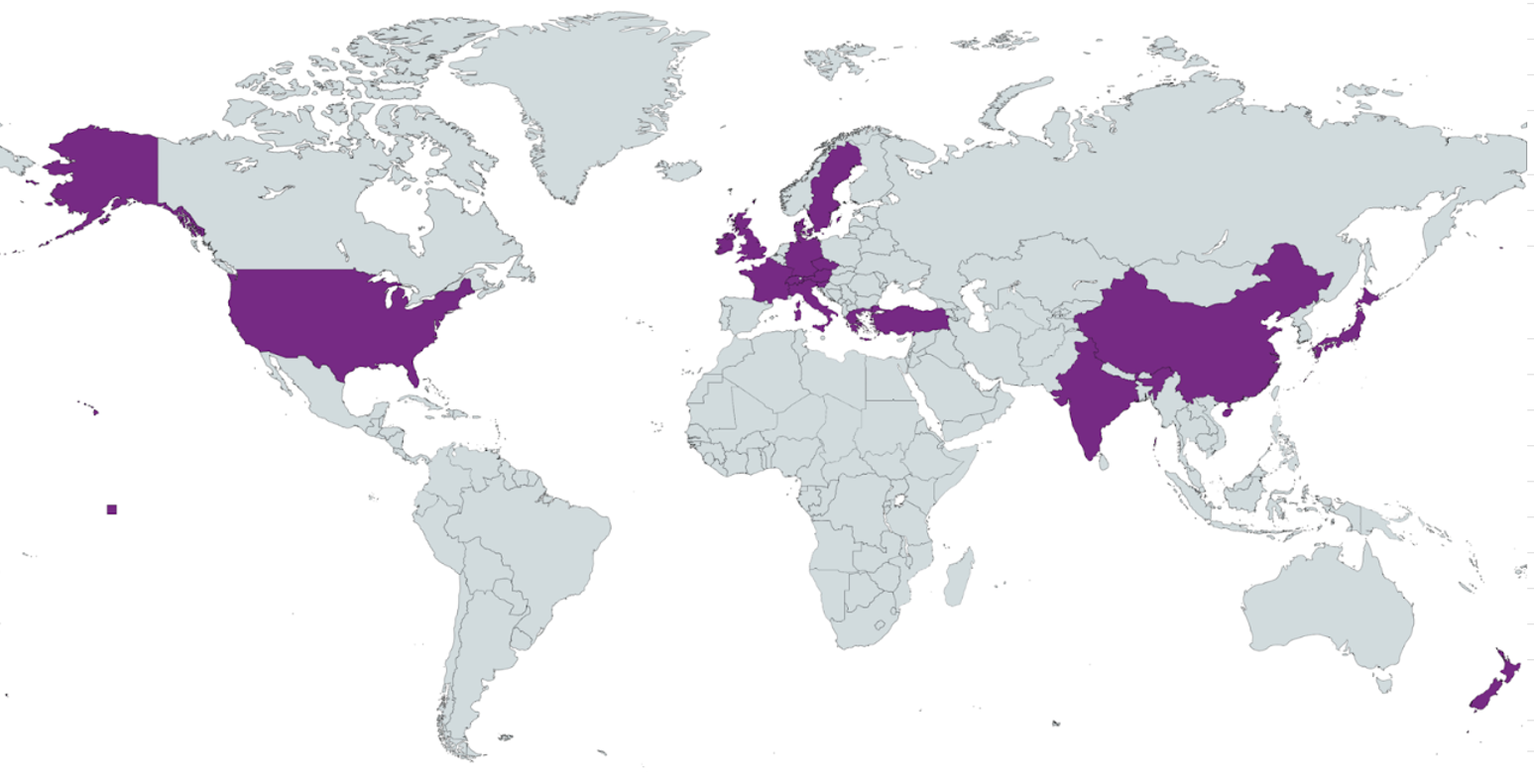

— World Engagement Map

Democritus University of Thrace

“This work was supported by a research grant from Codasip, a provider of customizable RISC-V IP and Codasip Studio design toolset, and its University Program to Democritus Univ. of Thrace for “RISCV vector processor design”.

Lund University:

“This endeavour would not have been possible without the collaboration with Codasip. Our sincere appreciation goes to Keith Graham and Tadej Murovič. Thank you for granting us access to essential resources and for providing valuable feedback during our research.”

Codasip University Program team

Blog

Read the latest Codasip Labs Blogs