The RISC-V’s open Instruction Set Architecture (ISA) has spurred the innovation of free software tools and application software. Many of these software developments are software “islands” that must be combined through scripts. With different tools from different sources, continual interoperability is at risk and there is a support cost of monitoring and updating their interoperability. The alternative is a single unified toolchain. The benefit of the unified approach is twofold. First, the obvious case in that the toolchain upgrades are validated before releases ensuring a functional toolchain reducing or eliminating the required monitoring of different tools and upgrading required scripts. The second benefit is not as obvious but may be the most important: through a single unified toolchain, researchers benefit from enhanced tools.

The Codasip’s University Program makes available Codasip Studio, a single unified toolchain for processor architecture’s ISA specifications, development of the processor’s hardware architecture, software development tools, to outputting RTL such as Verilog for FPGA and ASIC synthesis. The University Program has been developed to spur innovation in research and student curriculum. Let’s see, in this blog post, how Codasip Studio will benefit researchers and engineering students.

Single unified toolchain for processor development

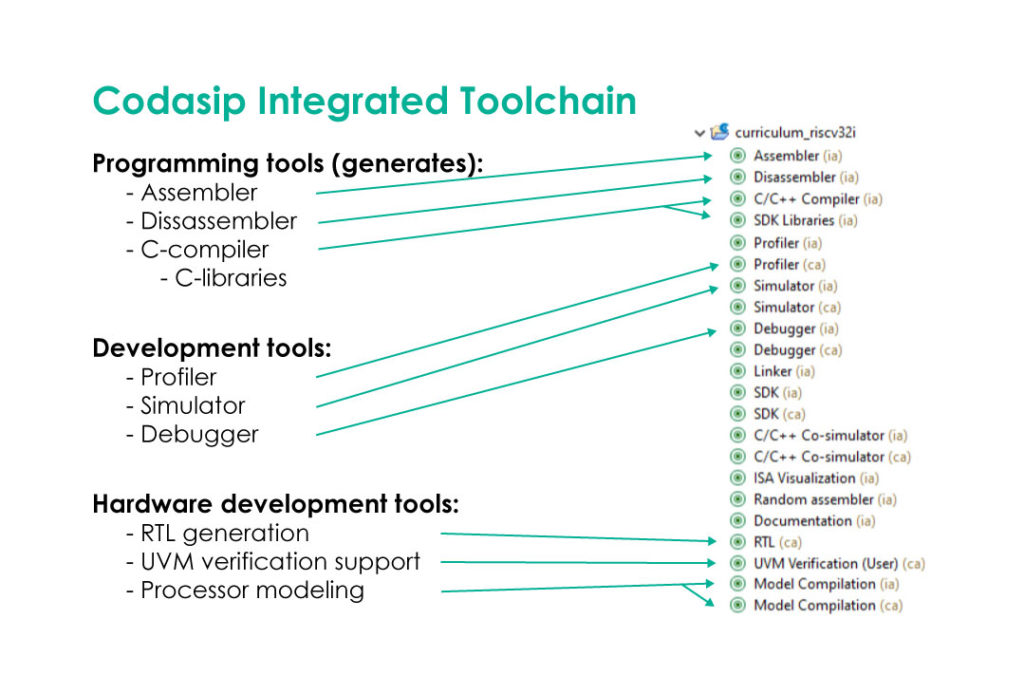

Codasip Studio outputs a Hardware Development Kit (HDK) and a Software Development Kit (SDK). The HDK includes all the tools and tasks to specify a processor’s Instruction Accurate (IA) model and implement it as a Cycle Accurate (CA) model. These models are specified using CodAL, a C-like processor description language that enables high-level synthesis description of both the IA and CA models. The SDK includes all the tools required for software application development starting at the assembler to linker, to C-compiler, to C-libraries, through software simulator.

As the status of these integrated development tools is aware of each other, as in a makefile software build, only the required tasks are built. For example, if you modify a file that changes the IA model and is shared with the CA model, all the tasks for both the IA and CA model will be marked as not built. Upon requesting a higher-level task to be built, all lower dependent tasks that are not built will be built first. A good example is the SDK (IA) task. If this task is built, all dependent tasks such as Model Compilation, Assembler, Disassembler, Profiler, Simulator, Debugger, C/C++ compiler, and SDK libraries will be built if necessary. No script development or toolchain maintenance required.

Enhanced tools through a Unified Toolchain

How can Codasip Studio’s unified toolchain enhance research? Tightly coupling application integration with program acceleration into a processor’s core is a new research domain. To make engineering decisions, data is required. Codasip Studio’s integrated Profiler can analyze a software application to determine where clock cycles are spent, enabling researchers to focus where new instructions can result in program acceleration through cycle count reduction.

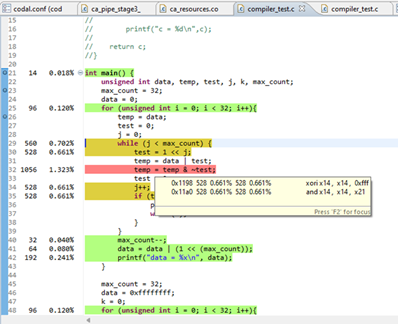

As in this example, the profiler annotates the C-program to highlight where clock cycles are spent, and the associated assembly sequence. The Researchers can minimize the original sequence into a single new instruction with the objective of not elongating the clock period.

RISC-V generated compiler realizes instruction acceleration

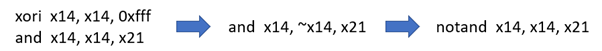

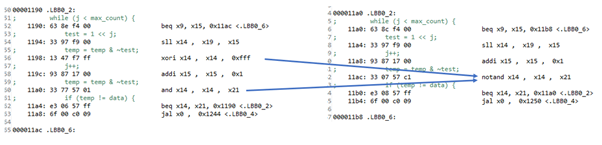

Creating new instructions for acceleration remains in the hypothetical sphere until it can be incorporated into useful applications. Codasip Studio compiler’s input is the processor’s IA model. Analyzing data from the profiler, researchers define a new instruction into the processor’s ISA, and upon rebuilding the SDK (IA), a compiler will be aware of the new instruction and use it in subsequent program builds.

From the program disassembly above, the newly added instruction has been incorporated into the compiler to replace the original two RISC-V instructions. Application acceleration has been achieved through cycle count reduction. The program cycle count can also be verified through running the updated program through the Profiler.

The entire process from initial application profiling, minimizing the instructions, to implementing a new instruction into the IA and CA models, and verification of program cycle count reduction can be achieved in an hour or two. The unified toolchain enables a very tight loop from data to concept to experimentation. With these short development cycles, researchers can easily experiment to find the optimal solution.

Get started with the University Program to explore Codasip Studio’s unified toolchain and how it can benefit your research in Program Security, Functional Safety, Artificial Intelligence, Real-Time Embedded Systems and other Domain Specific Architectures.