Custom Compute for Edge AI: Accelerating innovation with Lund University and Codasip University Program

In recent years, the rapid advancement and adoption of Artificial Intelligence (AI) on the edge has brought about a surge in development. As AI models like ChatGPT become more prevalent and accurate, the computational requirements for inference also escalate. This necessitates architectural innovations aimed at reducing both power consumption and latency. The need for edge […]

Functional safety in the automotive supply chain

By Dave Higham and Maricel Ventura Reliance on electronics and software is big business in the automotive industry and has driven significant focus on quality and reliability of vehicles and their components. Alongside this, the aim of safe, secure and accident-free driving has been given significant attention, with the publication of ISO 26262 for functional […]

A custom RISC-V vector instruction to accelerate structured-sparse matrix multiplications

A novel AI-acceleration paper presents a method to optimize sparse matrix multiplication for machine learning models, particularly focusing on structured sparsity. Structured sparsity involves a predefined pattern of zero values in the matrix, unlike unstructured sparsity where zeros can occur anywhere. The research was conducted by Democritus University of Thrace (DUTH) in Greece and was […]

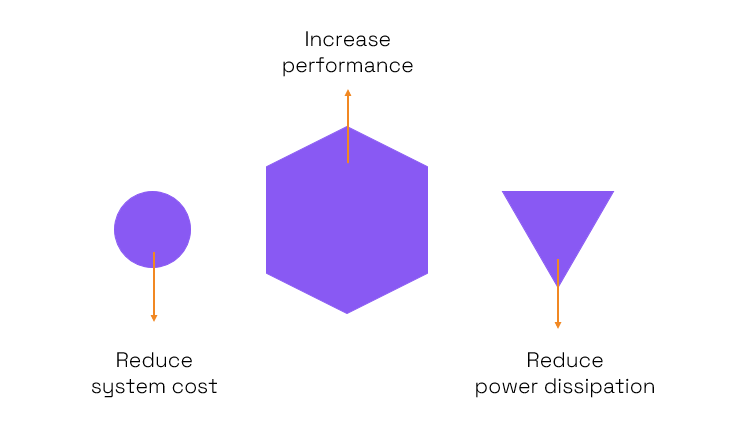

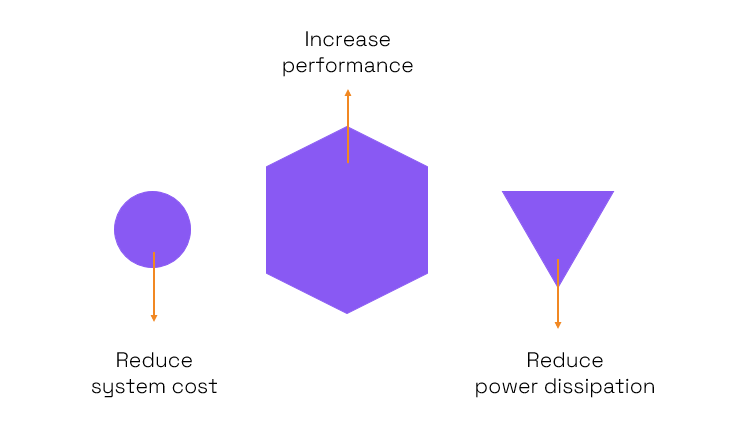

Unfair advantage? How OEMs get ahead with Custom Compute

Intro Original Equipment Manufacturers (OEMs) constantly face the challenge of delivering cutting-edge products that meet the evolving demands of their customers. In the world of technology, where innovation is the key to staying ahead, the choice of computing solutions plays a pivotal role in shaping the success of OEMs. In the past OEMs have relied […]

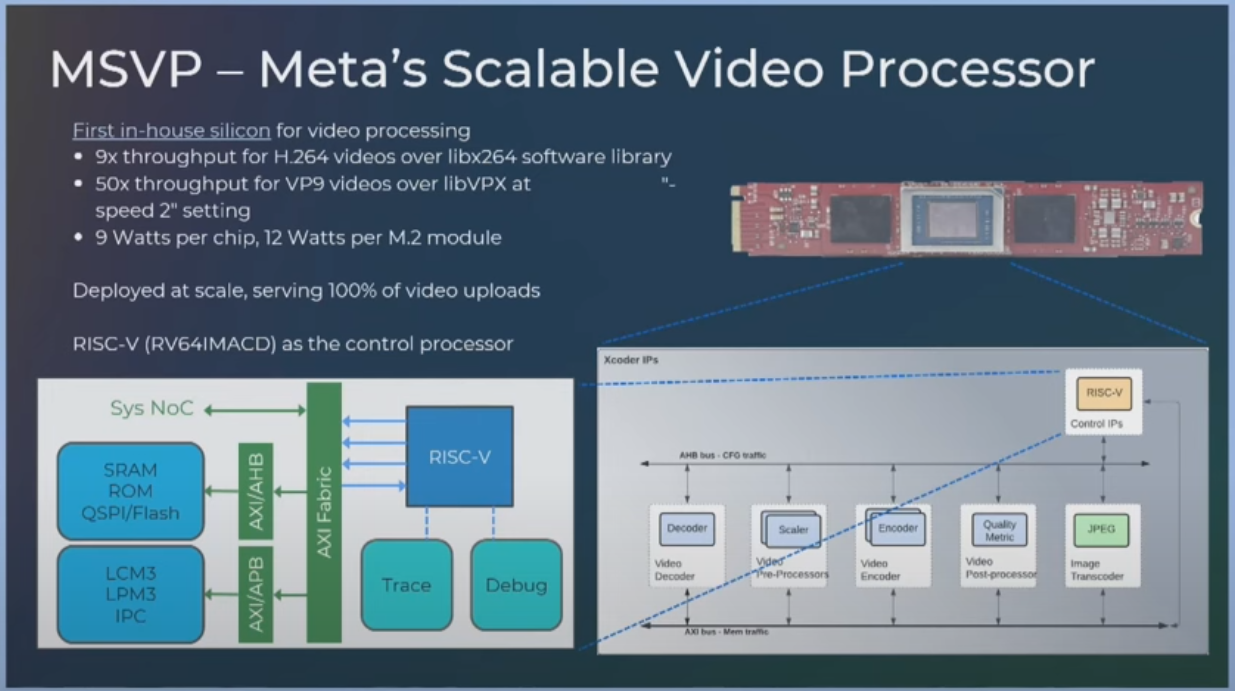

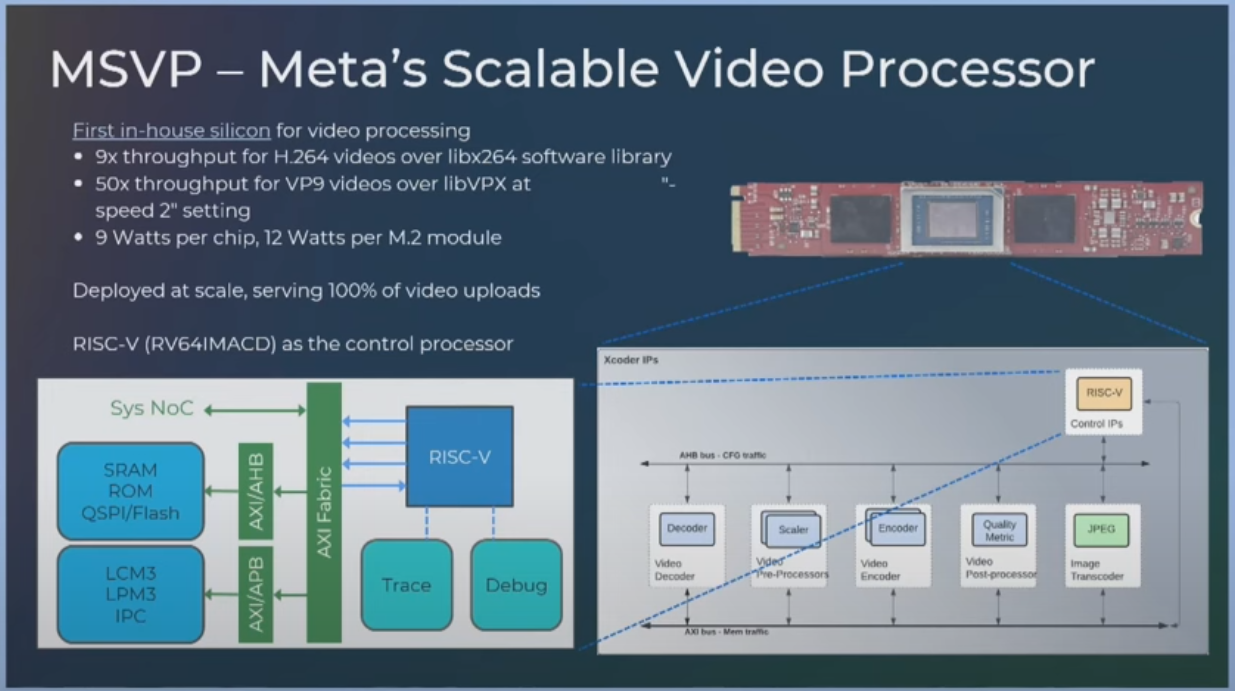

RISC-V Summit report: Meta leads the way for custom processors

As a regular attendee of the RISC-V Summit US, I’ve come to appreciate the unique blend of cutting-edge technology discussions and the sunny California weather. Indeed, a welcome departure for a Central European like myself, accustomed to slightly different climates. Of course, I attended lots of technical sessions as well as the keynotes. I could […]

It’s all about RISC-V code size

Here at Codasip we’re passionate about reducing the code size of our RISC-V cores for our customers, but why? Are we not making the core larger and more complex as we add instructions to improve the situation? In short the answer is yes we are, any instructions added to the processor increase the size, complexity, […]

5 reasons to attend RISC-V Summit Europe

The first-ever RISC-V Summit Europe will be held in Barcelona in June 2023! Enjoying the city at this time of the year is pretty amazing. The tapas, the beach, Las Ramblas, Gaudi’s architecture… We know. We will be there. As the European RISC-V leader. And here are 5 more reasons for you to be there […]

How to reduce the risk when making the shift to RISC-V

With the Intel® Pathfinder for RISC-V* program, Intel launched a development environment that enables companies of all sizes to start their RISC-V journey. Codasip makes its L31 RISC-V embedded core available to the embedded community through the program. We asked Vijay Krishnan, Intel Corporation, and Rupert Baines, CMO at Codasip, to tell us more about […]

5 good things about RISC-V

RISC-V has been around for some time now, and if you are here it’s because you have heard of it. But perhaps you still need to be convinced that it is the future? If you still wonder about its potential and benefits, here are 5 good things about RISC-V. 1. RISC-V IS AN OPEN STANDARD Let’s […]